# **Expanded Serial Peripheral Interface (xSPI) Industrial STT-MRAM Persistent Memory**

1.8V, 200MHz (STR & DTR) Octal SPI interface with SPI and QSPI

#### **Features**

- Expanded SPI bus interface supporting

- Octal, Quad, Dual, Single SPI protocol

- Up to 200MHz single and double transfer rate (STR/DTR) for Octal SPI

- Up to 133MHz, SPI, DSPI, QSPI

- Cycle endurance: Unlimited read, write and erase operations for supported life of product

- Data retention: 10 Years minimum across temperature

- JEDEC compliant: JESD251, JESD251-1

- Byte level writes and reads with no erase required as persistent memory

- Data integrity: No external ECC required.

- Low Power Modes:

- Standby

- Deep power down

- SPI compatibility: NVSRAM, FRAM, NOR, Toggle MRAM

- SPI, xSPI Commands for Program/Erase emulated NOR compatible Execute-in-place (XIP)

- Volatile and nonvolatile configuration settings

- Nonvolatile settings are not reflow protected

- Dedicated 256-byte OTP area outside main memory

- Readable and user-lockable

- Permanent lock with WRITE OTP command

- Not reflow protected

- Erase capability

- Chip(die) / bulk erase and sector erase

- Subsector erase 4KB, 32KB granularity

- Voltage

- 1.65 2.0V (1.8V)

- Density 128Mb

- 400MBps sustained throughput with OSPI at 200MHz, DTR, for reads and writes

- Boot mode configurations

- Boot in x1, x2, x4, x8

- Software reset and hardware reset pin available

- 3-byte and 4-byte address modes

- Sequential (burst) read and writes

- Electronic signature

- JEDEC-standard 3-byte signature

- JEDEC standard, RoHS compliant packages:

- 24-ball BGA, 6mm x 8mm (5 x 5 array)

- 8-pin DFN, 6mm x 8mm

- Operating temperature range

- Commercial: From 0°C to +70°C

- Industrial: From -40°C to +85°C

- Security and write protection

- 16 configurable hardware write protected regions plus top/bottom select

- Program/erase protection during power-up

- CRC command to detect accidental changes to user data

## **Table of Contents**

| Section | Content                                            |    |  |  |  |  |

|---------|----------------------------------------------------|----|--|--|--|--|

| 1       | Device Description with Block Diagrams             | 5  |  |  |  |  |

| 2       | Device Pin Assignments                             | 7  |  |  |  |  |

|         | 2.1 24-Ball BGA                                    |    |  |  |  |  |

|         | 2.2 Signal Ball Assignment                         |    |  |  |  |  |

|         | 2.3 8-Lead DFN Package                             |    |  |  |  |  |

|         | 2.4 DFN Signal Pinout                              |    |  |  |  |  |

| 3       | Signal Descriptions                                | 10 |  |  |  |  |

| 4       | xSPI Signal Protocol                               | 11 |  |  |  |  |

| 5       | Registers                                          | 13 |  |  |  |  |

|         | 5.1 Status Register                                |    |  |  |  |  |

|         | 5.2 Hardware Write Protection                      |    |  |  |  |  |

|         | 5.3 Flag Status Register                           |    |  |  |  |  |

|         | 5.4 Configuration Registers                        |    |  |  |  |  |

|         | 5.5 Nonvolatile Configuration Register             |    |  |  |  |  |

|         | 5.6 Volatile Configuration Register                |    |  |  |  |  |

|         | 5.7 Interrupt mask and Status Register             |    |  |  |  |  |

|         | 5.8 Device Factory Initialization Mode             |    |  |  |  |  |

|         | 5.9 Tuning Data Pattern Register                   |    |  |  |  |  |

|         | 5.10 Supported Clock Frequencies                   |    |  |  |  |  |

| 6       | Register Operations                                | 26 |  |  |  |  |

| 7       | Memory Organization                                | 31 |  |  |  |  |

| 8       | xSPI Commands and OpCodes                          | 32 |  |  |  |  |

| 9       | Read and Write Operations                          | 34 |  |  |  |  |

| 10      | READ Operations                                    | 35 |  |  |  |  |

| 11      | WRITE (Program) Operations                         | 42 |  |  |  |  |

| 12      | XIP (Execute-in-Place) Mode                        | 47 |  |  |  |  |

| 13      | ERASE Operations                                   | 49 |  |  |  |  |

| 14      | OTP Operation                                      | 50 |  |  |  |  |

| 15      | Extended Address Operation                         | 52 |  |  |  |  |

| 16      | Deep Power Down Operation                          | 54 |  |  |  |  |

| 17      | Initialization Considerations                      | 56 |  |  |  |  |

| 18      | Reset Operations                                   | 57 |  |  |  |  |

| 19      | Tuning Data Pattern                                | 60 |  |  |  |  |

| 20      | CRC                                                | 61 |  |  |  |  |

| 21      | Package Information                                | 63 |  |  |  |  |

| 22      | Electrical Specifications and Operating Conditions | 66 |  |  |  |  |

| 23      | Orderable Part Numbers                             | 77 |  |  |  |  |

|         | Revision History                                   | 78 |  |  |  |  |

## **List of Figures**

| Figure 1:  | Block Diagram                                              | 6  |

|------------|------------------------------------------------------------|----|

| Figure 2:  | Logic Diagram                                              | 6  |

| Figure 3:  | Device Pin Assignments 24-ball BGA                         | 7  |

| Figure 4:  | 8-Pin DFN Package Signal Assignments                       | 9  |

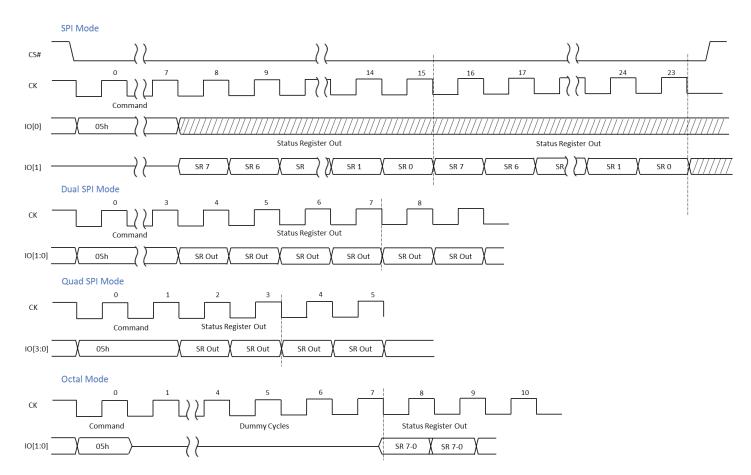

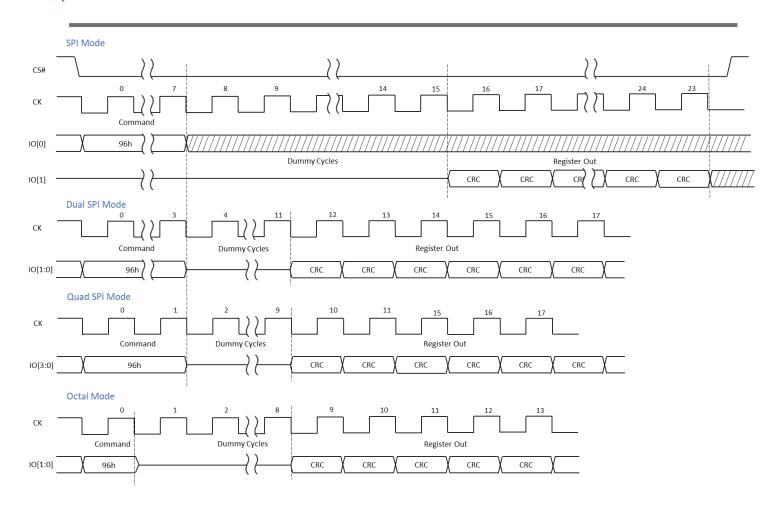

| Figure 5:  | READ Status Register with STR                              | 26 |

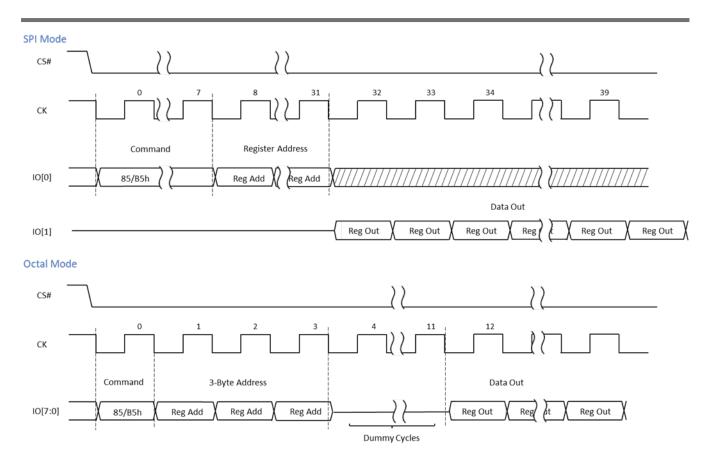

| Figure 6:  | Read Nonvolatile/Volatile Register                         | 27 |

| Figure 7:  | READ General Purpose Register with STR                     | 28 |

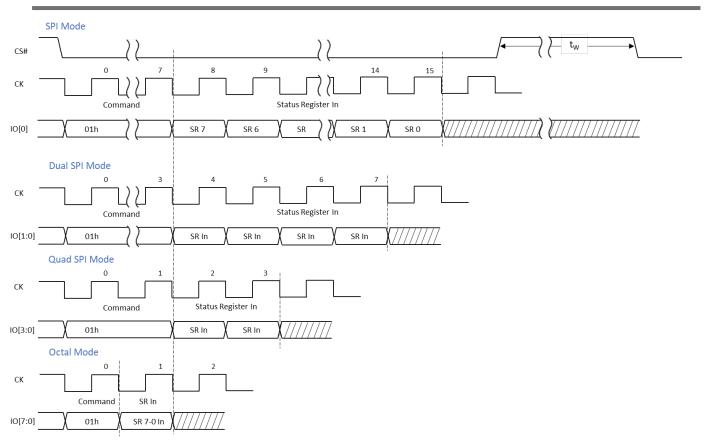

| Figure 8:  | Write Status Register                                      | 29 |

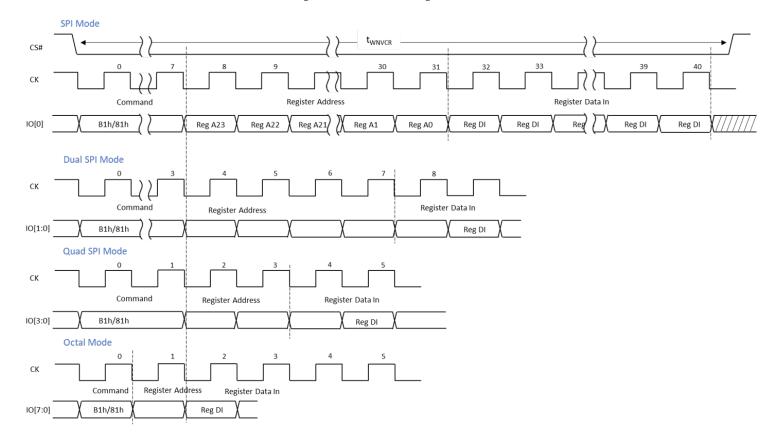

| Figure 9:  | Write Nonvolatile/Volatile Register                        | 30 |

| Figure 10: | Opcode Timing Diagram                                      | 34 |

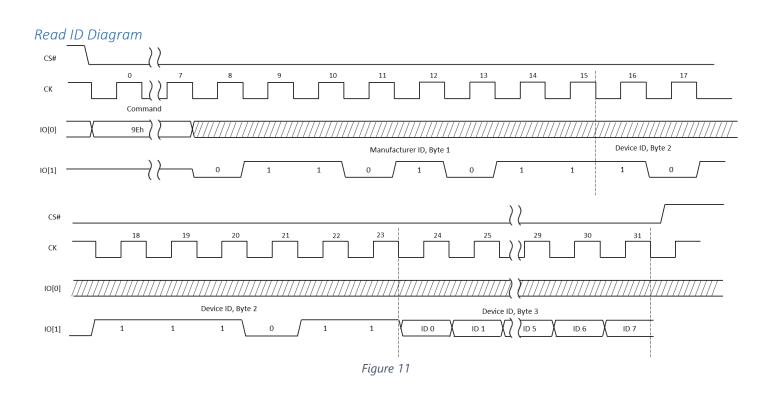

| Figure 11: | READ ID Diagram                                            | 36 |

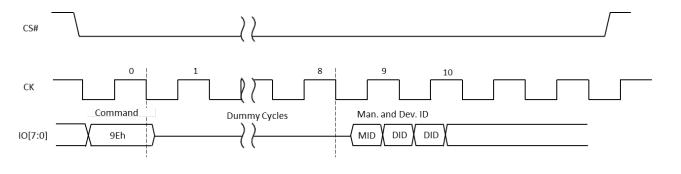

| Figure 12: | Read ID Diagram (Octal DTR Mode)                           | 36 |

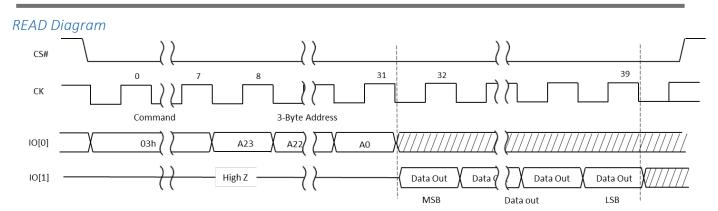

| Figure 13: | Read Diagram                                               | 38 |

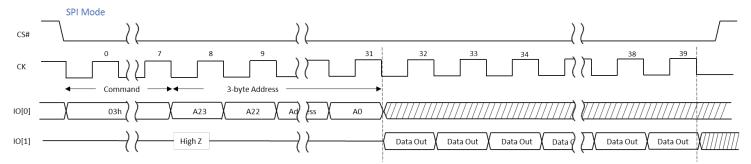

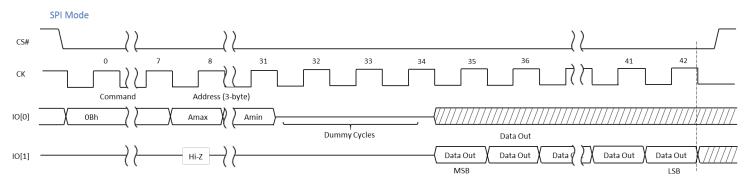

| Figure 14: | Read Fast Diagram                                          | 39 |

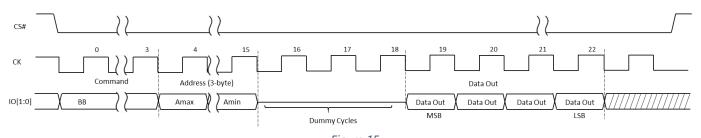

| Figure 15: | Read Fast Dual Input/Output                                | 39 |

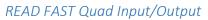

| Figure 16: | Read Fast Quad Input/Output                                | 39 |

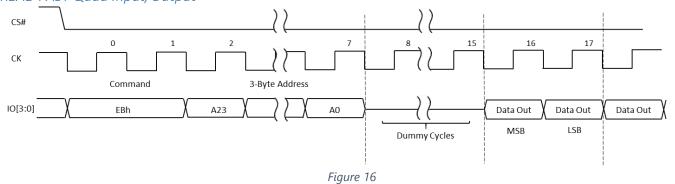

| Figure 17: | Read Fast Octal Output                                     | 40 |

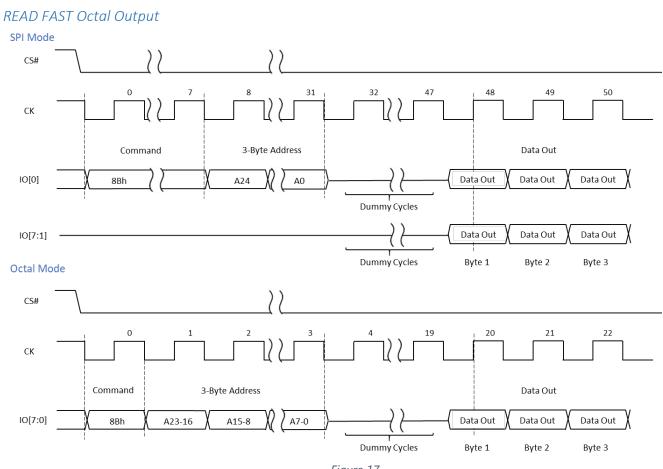

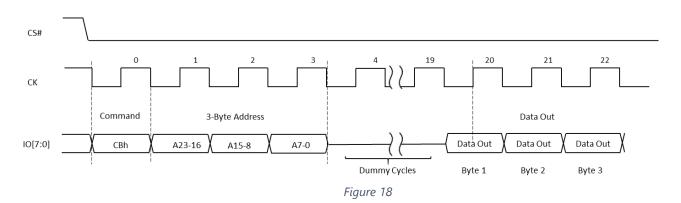

| Figure 18: | Read Fast Octal Input/Output                               | 40 |

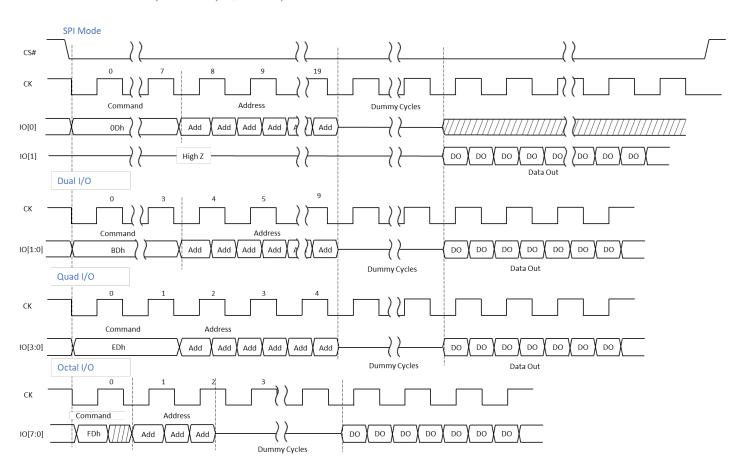

| Figure 19: | Read Fast DTR SPI, Dual SPI, Quad SPI, Octal SPI           | 41 |

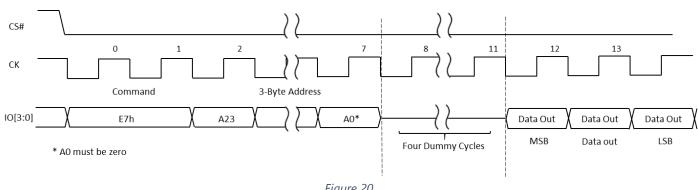

| Figure 20: | Read Word Quad Input/Output (no DTR) (E7h)                 | 41 |

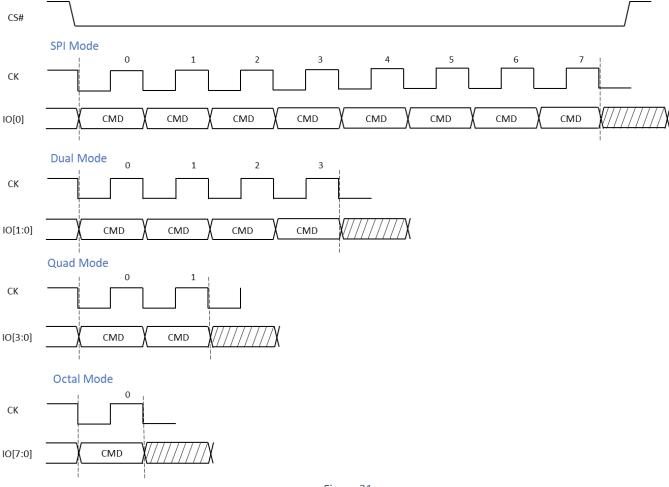

| Figure 21: | Write Enable/Disable Operation                             | 42 |

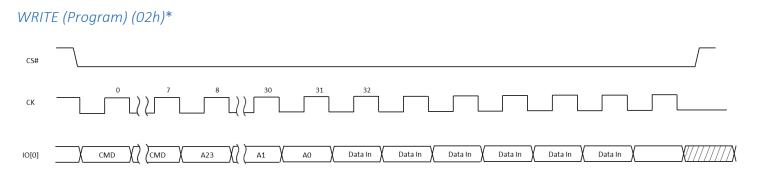

| Figure 22: | Write (Program)                                            | 44 |

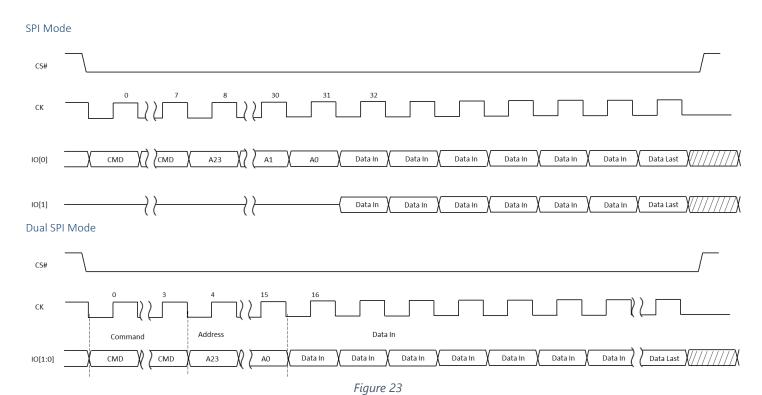

| Figure 23: | Write Fast Dual Input                                      | 44 |

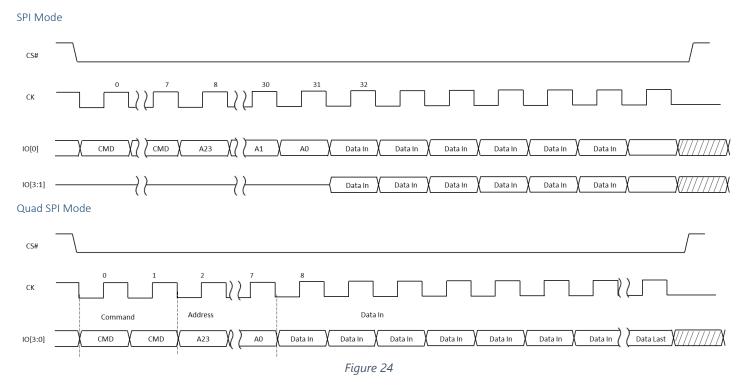

| Figure 24: | Write Fast Quad Input                                      | 45 |

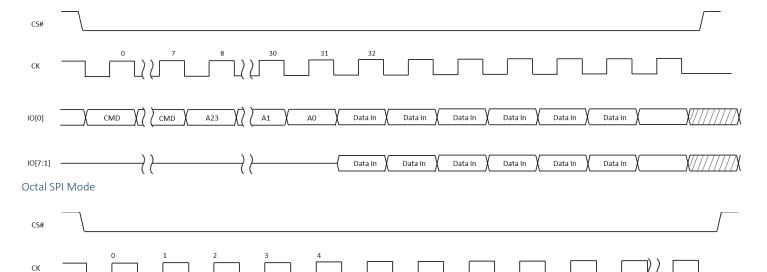

| Figure 25: | Write Fast Octal Input                                     | 45 |

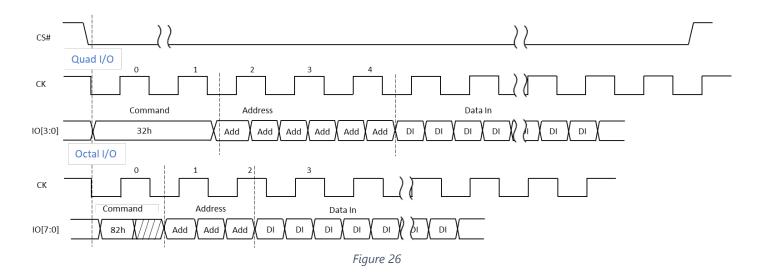

| Figure 26: | Write Fast with DTR Configured                             | 46 |

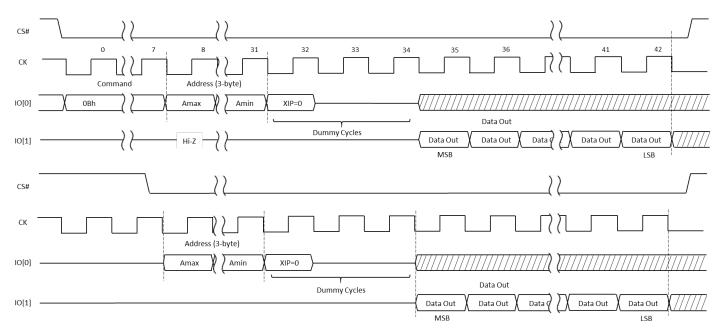

| Figure 27: | Read Fast (XIP)                                            | 48 |

| Figure 28: | Erase Operations                                           | 49 |

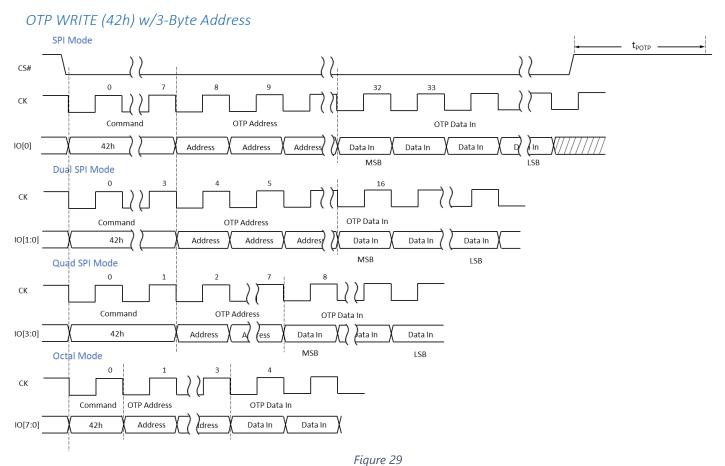

| Figure 29: | OTP Write                                                  | 51 |

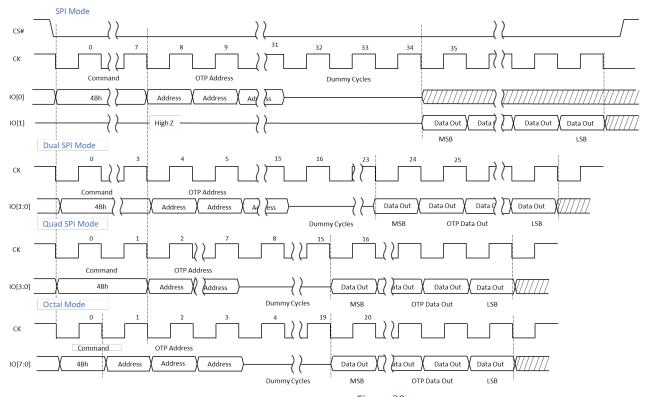

| Figure 30: | OTP Read                                                   | 52 |

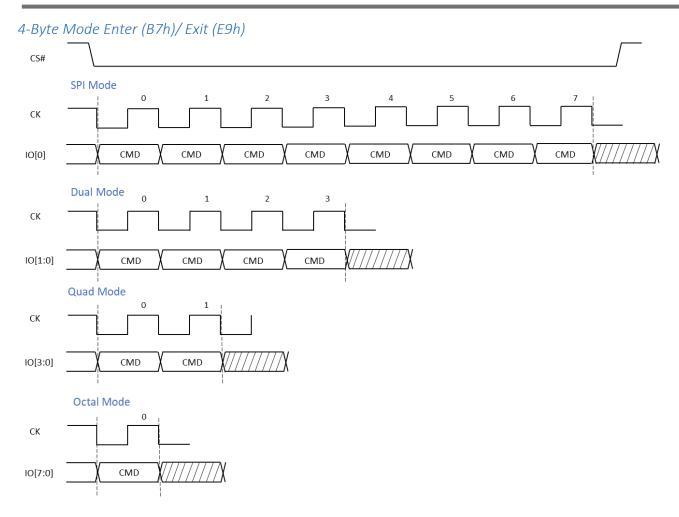

| Figure 31: | 4-Byte Address Mode Enter                                  | 53 |

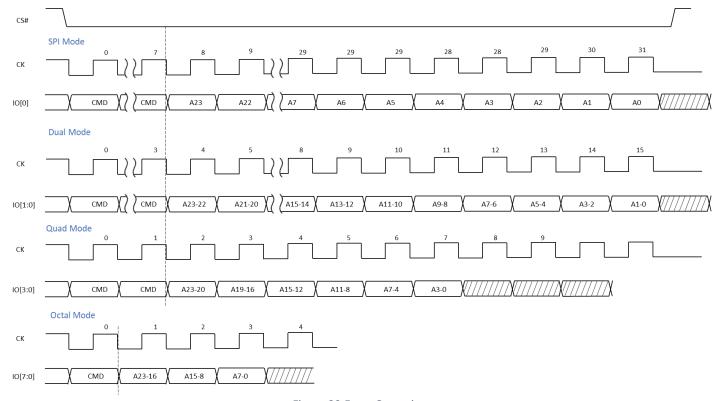

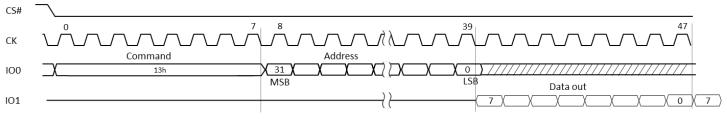

| Figure 32: | Read 4-Byte Address                                        | 54 |

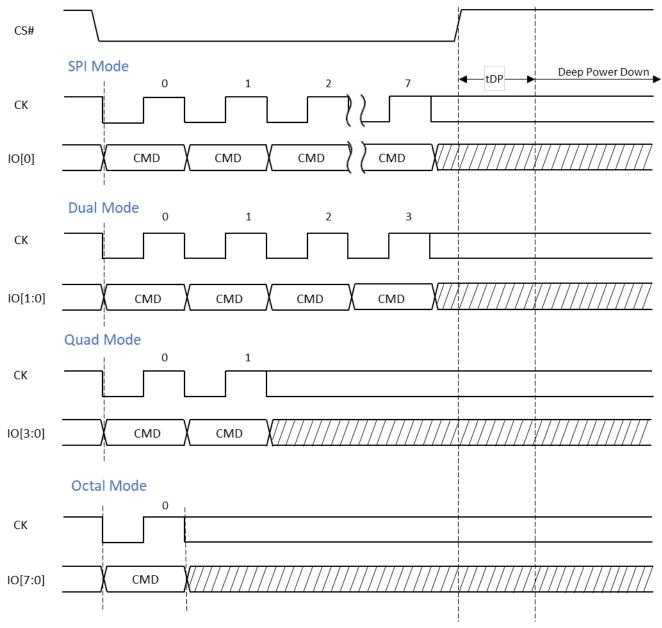

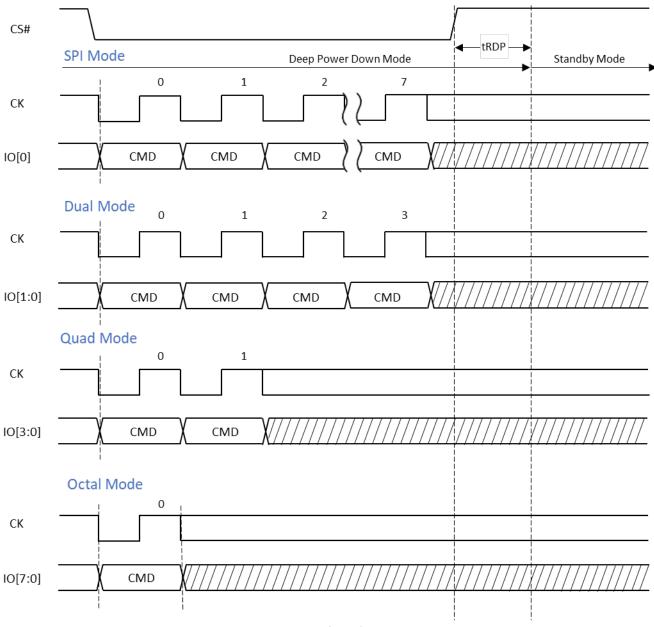

| Figure 33: | Deep Power Down Enter                                      | 56 |

| Figure 34: | Deep Power Down Exit                                       | 56 |

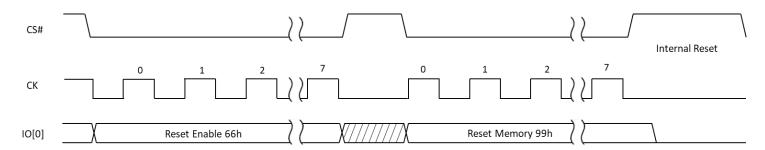

| Figure 35: | Software Reset                                             | 57 |

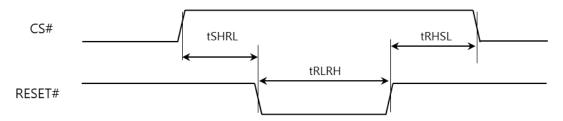

| Figure 36: | Hardware Reset Timing                                      | 58 |

| Figure 37: | Reset with Signal Sequence                                 | 59 |

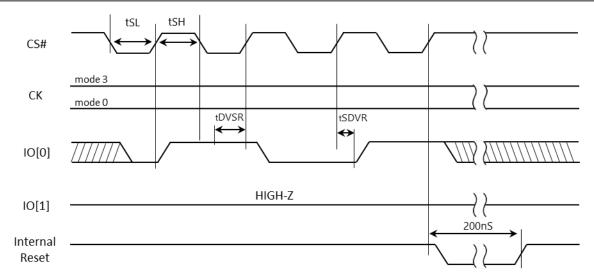

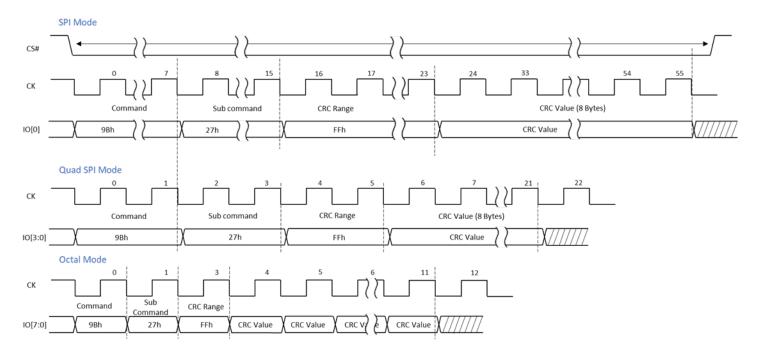

| Figure 38: | CRC Operation                                              | 62 |

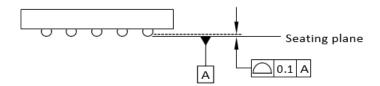

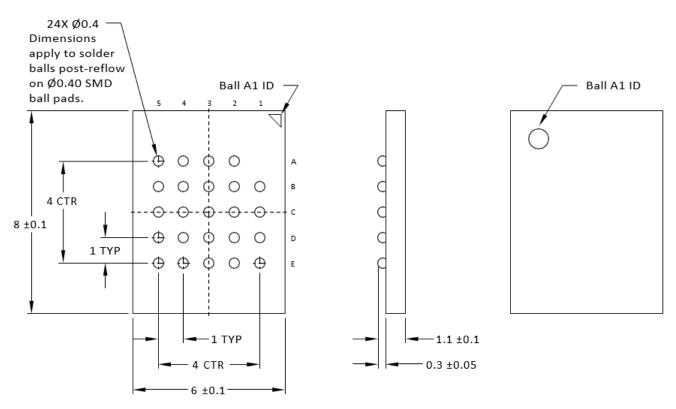

| Figure 39: | 24-Ball TBGA Package                                       | 63 |

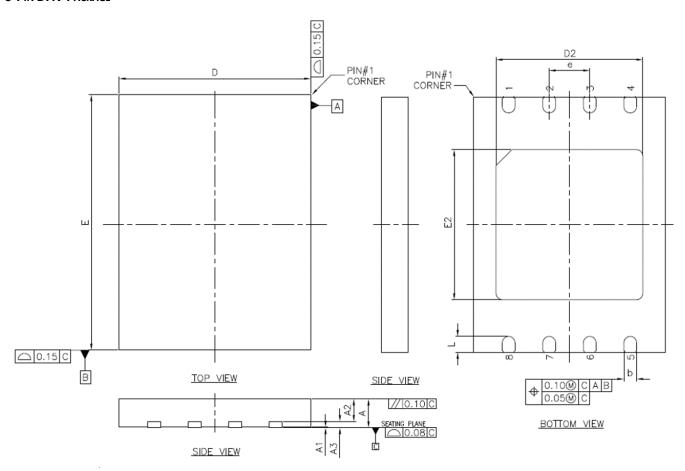

| Figure 40: | 8-PIN DFN Package                                          | 64 |

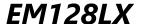

| Figure 41: | Power-On Timing                                            | 66 |

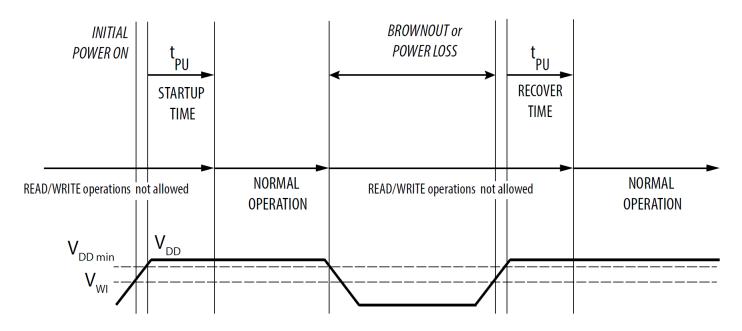

| Figure 42: | AC Timing Input/Output Reference Levels                    | 69 |

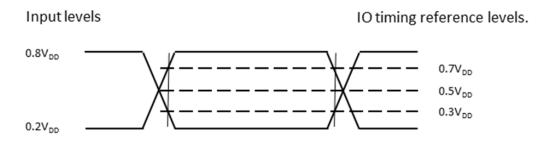

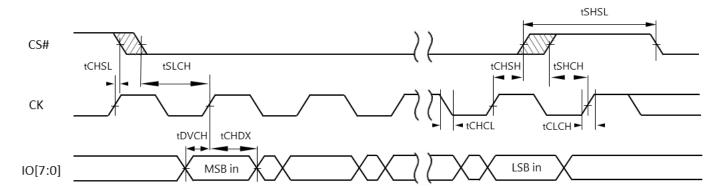

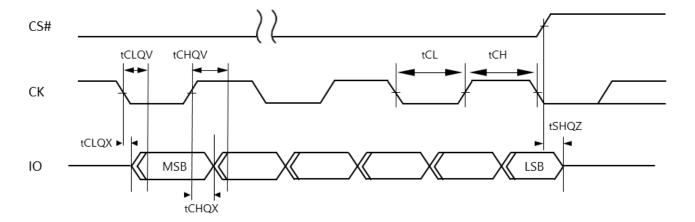

| Figure 43: | Serial Input Timing STR in SPI Mode                        | 73 |

| Figure 44: | Serial Input Timing STR in Dual, Quad, and Octal SPI Modes | 73 |

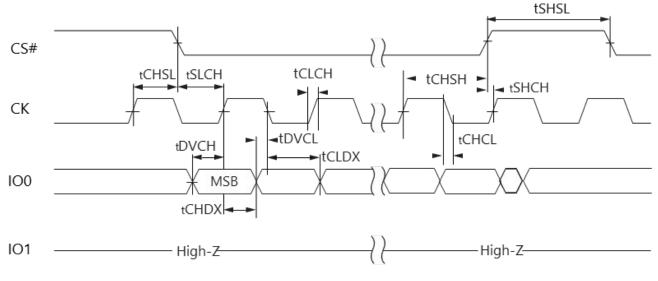

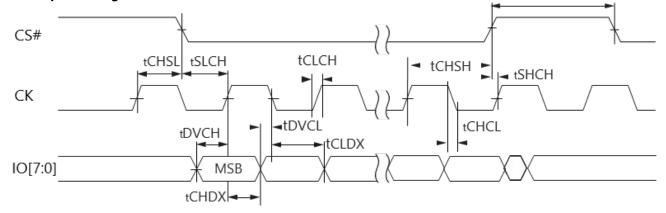

| Figure 45: | Serial Input Timing DTR in SPI Mode                        | 74 |

| Figure 46: | Serial Input Timing DTR in Dual, Quad, or Octal SPI Mode   | 74 |

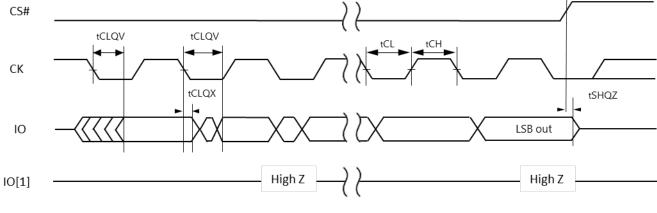

| Figure 47: | Serial Output Timing STR                                   | 75 |

| Figure 48: | Serial Output Timing DTR                                   | 75 |

| Figure 49: | Data Strobe (DS) Timing                                    | 76 |

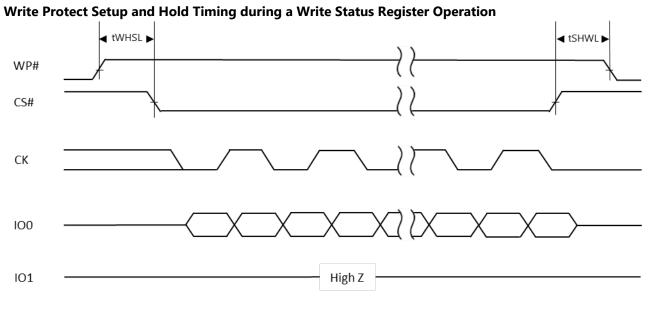

| Figure 50: | Write Protect Setup and Hold Timing                        | 76 |

## **List of Tables**

| Table 1:              | Signal Ball Assignments 24 Ball BGA | . 8  |

|-----------------------|-------------------------------------|------|

| Table 2:              | Signal Pinout 8-DFN                 | . 9  |

| Table 3:              | Signal Descriptions                 | . 10 |

| Table 4:              | 1S-1S-1S Bit Positions              | . 12 |

| Table 5:              | 8D-8D-8D Bit Positions              | . 12 |

| Table 6:              | Status Register                     | . 13 |

| Table 7:              | Write Protection                    | . 15 |

| Table 8:              | Block Protection                    | . 15 |

| Table 9:              | Flag Status Register                | . 16 |

| Table 10:             | Nonvolatile Configuration Register  | . 19 |

| Table 11:             | Volatile Configuration Register     | 21   |

| Table 12:             | Interrupt Mask                      |      |

| Table 13:             | Interrupt Status                    | . 22 |

| Table 14:             | Device Factory Initialization Mode  | . 23 |

| Table 15:             | TDP Register                        | . 23 |

| Table 16:             | Die Select Register                 | . 23 |

| Table 17:             | Supported Clock Frequency           | 25   |

| Table 18:             | Read Register Operations            | . 26 |

| Table 19:             | Write Register Operations           | . 29 |

| Table 20:             | Memory Organization                 | . 31 |

| Table 21:             | Instruction Command Table           | 34   |

| Table 22:             | Device ID Data                      | 35   |

| Table 23:             | XIP Bit Settings                    | . 47 |

| Table 24:             | Hardware Reset Timing               | . 58 |

| Table 25:             | CRC operation on entire device      | . 61 |

| Table 26:             | CRC operation on a range            | . 62 |

| Table 27:             | Power-On Timing                     | . 66 |

| Table 28:             | Absolute Maximum Ratings            | . 67 |

| Table 29:             | Recommended Operating Conditions    | . 67 |

| Table 30:             | Device Pin Loading                  | . 68 |

| Table 31:             | AC IO Timing Conditions             | . 68 |

| Table 32:             | DC Current Characteristics          | 68   |

| Table 33:             | DC Voltage Characteristics          | . 69 |

| Table 34 <sup>.</sup> | AC Specifications                   | 70   |

## 1. Device Description

The EM128LX is the industry's first xSPI serial interface persistent memory based on Everspin's unique industrial STT MRAM technology. It is a high-performance, multiple I/O, SPI-compatible MRAM device featuring a high-speed, low pin count SPI compatible bus interface with a clock frequency of up to 200 MHz and a single 1.8V power supply.

The **EM128LX** brings a new era of universal memory applications, replacing products such as SRAM, BBSRAM, NVSRAM and over-provisioned NOR devices and targets applications in Industrial Automation, Datacenter, Engineering Emulation, Automotive and Transportation, and Gaming. It is a great choice for the following application usage models:

Scramming Memory

Continuous Ring Buffers

**Data Logging**

Write Buffer

Journaling

Code Storage & Execution (+XIP)

Boot Load Configuration

Data RAM

Instant FPGA Re-Configurability

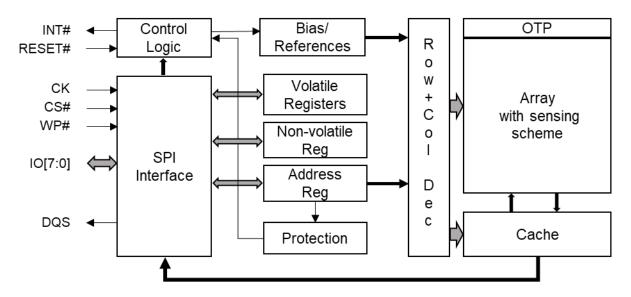

### **BLOCK DIAGRAM**

Figure 1

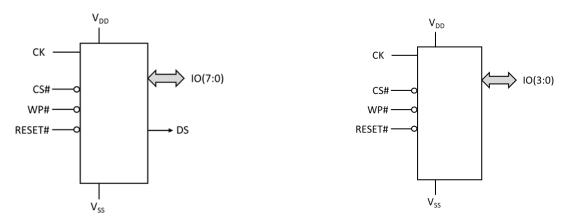

### LOGIC DIAGRAM

OSPI, QSPI, DSPI, xSPI (24-PIN BGA)

**QSPI, DSPI, SPI (8-PIN DFN)**

Figure 2

## 2. Device Pin Assignments

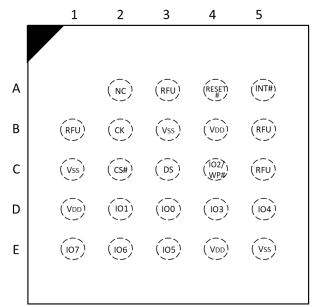

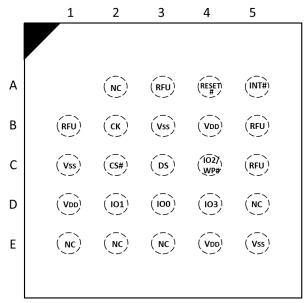

## 2.1 24-BALL BGA, 5 x 5 (BALLS DOWN)

Figure 3a Octal SPI with Quad, Dual and Single SPI modes

Figure 3b Quad SPI with Single SPI mode

## 2.2 SIGNAL BALL ASSIGNMENT

| TABLE 1: 24 BALL BGA XSPI, OCTAL, QI | uad, Dual and Single |

|--------------------------------------|----------------------|

| SPI Modes                            |                      |

| Ball Location | xSPI Signal     | Ball Location | xSPI Signal     |

|---------------|-----------------|---------------|-----------------|

| A1            | No Ball         | C4            | IO2 / WP#       |

| A2            | NC              | C5            | RFU             |

| А3            | RFU             | D1            | V <sub>DD</sub> |

| A4            | RESET#          | D2            | IO1             |

| A5            | INT#            | D3            | 100             |

| B1            | RFU             | D4            | IO3             |

| B2            | CK              | D5            | 104             |

| В3            | V <sub>SS</sub> | E1            | 107             |

| B4            | V <sub>DD</sub> | E2            | IO6             |

| B5            | RFU             | E3            | IO5             |

| C1            | V <sub>SS</sub> | E4            | V <sub>DD</sub> |

| C2            | CS#             | E5            | V <sub>SS</sub> |

| C3            | DS              |               |                 |

#### Notes:

- The signals which show a "/" indicates that the pin or ball is dual function

- For C4 pin, the write protect feature (WP#) can only be used when device is in single SPI mode

- See WP# signal description for detail

Table 1

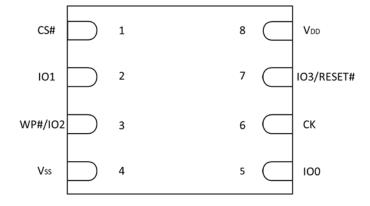

### 2.3 8-PIN DFN PACKAGE

Figure 4 3

## 2.4 SIGNAL PINOUT

TABLE 2: QUAD, DUAL AND SINGLE SPI MODES

| Pin Location | Signal          |

|--------------|-----------------|

| 1            | CS#             |

| 2            | IO1             |

| 3            | WP#/IO2         |

| 4            | V <sub>SS</sub> |

| 5            | 100             |

| 6            | CK              |

| 7            | IO3/RESET#      |

| 8            | V <sub>DD</sub> |

#### Note:

- Pin 7 will be IO3 in Quad SPI mode and RESET# in SPI mode or Dual SPI mode.

- When using SPI and Dual SPI commands, IO3

must be driven high before CS# goes high to

avoid an unintended reset.

Table 2

## 3. **Signal Descriptions**

| Signal<br>Name  | Туре                   | Description                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#             | Input                  | <b>Chip Select.</b> Bus transactions are initiated with a HIGH to LOW transition. Bus transactions are terminated with a LOW to HIGH transition.                                                                                                                                                                                                                                   |

| CK              | Input                  | <b>Clock.</b> Command, Address and Data information is transferred from controller to memory with respect to the rising or falling edge of the CK. The clock is not required to be free running.                                                                                                                                                                                   |

| IO[7:0]         | Input / Output         | <b>Data Input/Output.</b> Command, Address, and Data information is transferred on these signals during Read and Write transactions.                                                                                                                                                                                                                                               |

| DS              | Output                 | <b>Data Strobe.</b> Strobe signal to capture read data sent by the memory. DS is used by a limited set of xSPI commands.                                                                                                                                                                                                                                                           |

| V <sub>DD</sub> | Power Supply           | Power.                                                                                                                                                                                                                                                                                                                                                                             |

| VSS             | Power Supply           | Ground.                                                                                                                                                                                                                                                                                                                                                                            |

| RESET#          | Input                  | <b>Hardware Reset.</b> When LOW, the memory will self-initialize and return the device to the ready state. DS and IO[7:0] are placed into the High-Z state when RESET# is LOW. The RESET# signal should not be allowed to float; an external pull-up should be used on the PCB for a BGA package. IO3 and RESET# share Pin 7 in the DFN package. See section 18.2 for more detail. |

| INT#            | Output<br>(Open Drain) | <b>Interrupt</b> . When LOW, the memory indicates that an internal event has occurred. This signal is intended to be used as a system level interrupt for the device to indicate that an on-chip event has occurred. INT# is an open-drain output.                                                                                                                                 |

| WP#             | Input                  | <b>Write Protect</b> . Locks the status register in conjunction with the enable/disable bit [7] of the status register. This signal does not have internal pull-ups, it cannot be left floating and must be driven, even if neither of WP#/IO2 function is used.                                                                                                                   |

| RFU             | Undefined              | <b>Reserved for Future Use.</b> The package terminal may be connected to a circuit in the device. The function of the terminal is not currently defined or may be used for an optional signal. It is recommended to leave the terminal open and unconnected to external circuits.                                                                                                  |

| NC              | No Connection          | No Connection. The package terminal has no connection to circuits in the device.                                                                                                                                                                                                                                                                                                   |

| DNU             | Undefined              | <b>Do Not Use.</b> The package terminal must remain open and unconnected to external circuits.                                                                                                                                                                                                                                                                                     |

Table 3

## 4. xSPI Signal Protocol

During the time that CS# is active (LOW) the clock signal (CK) is toggled while command information is first transferred on the data (IO) signals. The clock must be active during any period required for information access or transfer to the memory. The clock continues active during the transfer of read data from the memory to the controller or write data from the controller to the memory. When the controller has transferred the desired amount of data, CS# is driven inactive (HIGH). The period during which CS# is active is called a transaction on the bus.

While CS# is inactive, the CK is not required to toggle. CK may stop toggling when CS# is LOW as a means of lowering power consumption or inserting delay within a transaction for flow control. CK must always complete at least one rising edge and one falling edge before stopping at LOW. This requirement for a minimum of one rising and falling edge in turn requires that DTR transfers always occur in two transfer increments, e.g., two bytes (word) for 8-bit wide transfers in 8D mode. STR transfers must occur in one byte increments.

There are up to four phases of activity within each transaction:

- Command transfer from controller to memory

- **Command Modifier** (Address) transfer from controller to memory

- Initial Access Latency (also used for IO signal direction turn around in a read transaction)

- **Data transfer** (memory to controller in a read transaction or controller to memory in a write transaction)

The command transfer occurs at the beginning of every transaction. The command modifier, initial access latency, and data transfer phases are optional, and their presence depends on the protocol mode or command transferred. The number of parallel IO signals used during the command modifier and data phases depends on the current protocol mode or command transferred. The initial access latency phase does not use the IO signals for information transfer. The protocol mode options are described by the data rate and the IO width (number of IO signals) used during the command, command modifier (address), and data phases in the following nomenclature (format):clock

WR-WR-WR where:

The first *WR* is the command bit width and rate

The second *WR* is the command modifier (address) bit width and rate

The third *WR* is the data bit width and rate.

The bit width W value may be 1, 2, 4 or 8. R has a value of S for STR, or D for DTR. STR has the same transfer value during the rising and falling edge of a clock cycle. DTR may have different transfer values during the rising and falling edges of each clock.

1S-1S-1S means that the command is 1-bit wide STR, the command modifier is 1-bit wide STR, and the data is one bit wide STR. 8D-8D-8D means that the command, the command modifier, and data transfers are always 8 bits wide DTR. The EM128LX uses the option to repeat the command opcode which makes an 8D command look like an 8S command, but it is not required to repeat the command opcode.

Example protocol modes supported for the EM128LX are:

1S-1S-1S; 1S-1D-1D

2S-2S-2S; 2S-2D-2D

4S-4S-4S; 4S-4D-4D

8S-8S-8S; 8D-8D-8D

**Note**: For full list of opcodes and modes supported by EM128LX, please refer to section "xSPI Command Opcodes and Modes".

The EM128LX must be configured during the factory initialization to select the mode in which the device will boot following Power-On-Reset (POR). Supported boot modes are x1, x2, x4 or x8. For example, 8S-8D-8D mode can be made the default mode if so desired. The controller must determine the default protocol mode of the memory after POR. This may be done through prior knowledge of the system design. The controller may later reconfigure the memory to use other supported modes.

A protocol mode phase using single bit transfer uses IO[0] to transfer information from controller to memory and IO[1] to transfer information from memory to controller. On each IO, information is placed on the IO line in Most Significant bit (MSb) to Least Significant bit (LSb) order within each byte. Sequential command modifier bytes are transferred in highest order to lowest order sequence. Sequential data bytes are transferred in lowest address to highest address order.

| Ю | Command Bits           | Command Modifier Bits (address) | Latency Data Byte 0 |                        | Data Byte 1            |

|---|------------------------|---------------------------------|---------------------|------------------------|------------------------|

| 0 | 7, 6, 5, 4, 3, 2, 1, 0 | 31 (23), 30 (22), 1, 0          | X                   | X                      | X                      |

| 1 | X                      | X                               | X                   | 7, 6, 5, 4, 3, 2, 1, 0 | 7, 6, 5, 4, 3, 2, 1, 0 |

| 2 | X                      | X                               | X                   | X                      | X                      |

| 3 | X                      | X                               | X                   | X                      | X                      |

| 4 | X                      | X                               | X                   | X                      | X                      |

| 5 | X                      | X                               | X                   | X                      | X                      |

| 6 | X                      | X                               | X                   | X                      | X                      |

| 7 | X                      | X                               | X                   | X                      | X                      |

Table 4: 1S-1S-1S Bit Positions for 4 (and 3) Byte addressing

Table 4

A protocol mode phase using two IO signals uses IO[1:0], four IO signals using IO[3:0] and eight IO signals uses IO[7:0]. The LSb of each byte is placed on IO[0] with each higher order bit on the successively higher numbered IO signals. Sequential command modifier bytes are transferred in highest order to lowest order sequence. Sequential data bytes in STR are transferred in lowest address to highest address order. While in 8D mode, the sequential data bytes in DTR are transferred only in byte pairs (words) where the byte order depends on the order in which the bytes are written or programmed in that protocol mode. Sequential data bytes are transferred in lowest address to highest address order. In 8D mode, the starting address must be even.

| Ю | Command Bits |   | Command Modifier Bits<br>(command ext. & address) |    |    | Latency | Data W | ord 0 | Data W | ord 1 |   |

|---|--------------|---|---------------------------------------------------|----|----|---------|--------|-------|--------|-------|---|

| 0 | 0            | 0 | 24                                                | 16 | 8  | 0       | X      | 0     | 0      | 0     | 0 |

| 1 | 1            | 1 | 25                                                | 17 | 9  | 1       | X      | 1     | 1      | 1     | 1 |

| 2 | 2            | 2 | 26                                                | 18 | 10 | 2       | X      | 2     | 2      | 2     | 2 |

| 3 | 3            | 3 | 27                                                | 19 | 11 | 3       | X      | 3     | 3      | 3     | 3 |

| 4 | 4            | 4 | 28                                                | 20 | 12 | 4       | X      | 4     | 4      | 4     | 4 |

| 5 | 5            | 5 | 29                                                | 21 | 13 | 5       | X      | 5     | 5      | 5     | 5 |

| 6 | 6            | 6 | 30                                                | 22 | 14 | 6       | X      | 6     | 6      | 6     | 6 |

| 7 | 7            | 7 | 31                                                | 23 | 15 | 7       | X      | 7     | 7      | 7     | 7 |

Table 5: 8D-8D-8D Bit Positions for 4 (and 3) Byte addressing

Table 5

IO signals not in use in a particular phase are undefined and may or may not be driven by the controller or memory, i.e., these signals may be in a high impedance state (floating and indicated by X in the bit position tables).

#### Note:

- In single and dual bit transfers the IO[7:2] signals may be high impedance, unless they are dual purpose such as WP# or RESET# in the DFN package

- In quad bit transfers the IO[7:4] signals may be high impedance

During the data transfer period of a read memory transaction, the Data Strobe (DS) signal is driven by the memory device and transitions edge aligned with the IO signal data transitions. DS is used as an additional output signal with the same timing characteristics as other data outputs but with the guarantee of transitioning with every data bit transferred. The DS signal transitions can be received and internally phase shifted by the controller to be used as an internal read clock/strobe to capture each data bit transferred. Data Strobe is the return of the clock, CK. It is available in all modes and makes it easier to achieve higher clock frequencies. It is required to achieve the maximum clock frequencies. DS goes low when CS# is driven low by the host controller and is driven until CS# is pulled high. DS stays low while the device is receiving command, address, and data. DS will toggle while the device is transmitting data out.

## 5. Registers

The EM128LX supports various status and configuration registers for device status updates and configuration settings. These registers and their access details are discussed in the following sections.

#### 5.1 STATUS REGISTER

Read Status Register or Write Status Register commands are used to read from or write to the Status Register bits, respectively. When the status register enable/disable bit (bit 7) is set to 1 and WP# is driven LOW, the status register nonvolatile bits become read-only and the Write Status Register operation will not execute. This hardware-protected mode is exited by driving WP# high.

|     | Status Register         |                                   |                                                                                                                                                                                                                                                                                      |                  |       |  |  |  |

|-----|-------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|--|--|--|

| Bit | Name                    | Settings                          | Description                                                                                                                                                                                                                                                                          | Туре             | Notes |  |  |  |

| 0   | WIP: Write in progress  | 0 = Ready<br>1 = Busy             | Status bit to determine if a Write Status Register,<br>Write Nonvolatile Configuration Register, Write<br>(Program), CRC, or Erase operation is in progress.<br>This bit is Read Only.                                                                                               | Volatile         | 2     |  |  |  |

| 1   | WEL: Write enable latch | 0 = Clear (Default)<br>1 = Set    | The device powers up with the Write enable latch (WEL) cleared to prevent inadvertent Write (Program), or Erase operations. To enable these operations, the Write Enable command must be executed to set this bit. The Write Disable command clears this bit. This bit is Read Only. | Volatile         |       |  |  |  |

| 2   | BP[0]                   | Refer to Protected<br>Area tables | Defines memory area to be software protected against Write (Program) or Erase operations. When one or more block protect bits are set to 1, a designated memory area is protected. This bit is writable.                                                                             | Non-<br>volatile | 1     |  |  |  |

| 3   | BP[1]                   | Refer to Protected<br>Area tables | Defines memory area to be software protected against Write (Program) or Erase operations. When one or more block protect bits are set to 1, a designated memory area is protected. This bit is writable.                                                                             | Non-<br>volatile | 1     |  |  |  |

| 4 | BP[2]                                   | Refer to Protected<br>Area tables     | Defines memory area to be software protected against Write (Program) or Erase operations. When one or more block protect bits are set to 1, a designated memory area is protected. This bit is writable. | Non-<br>volatile | 1 |

|---|-----------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---|

| 5 | Top/Bottom                              | 0 = Top (Default)<br>1 = Bottom       | Determines whether the top or bottom of the memory array is where the protected area as defined by the block protect bits starts from. This bit is writable.                                             | Non-<br>volatile |   |

| 6 | BP[3]                                   | Refer to Protected<br>Area tables     | Defines memory area to be software protected against Write (Program) or Erase operations. When one or more block protect bits are set to 1, a designated memory area is protected. This bit is writable. | Non-<br>volatile | 1 |

| 7 | Status Register Write<br>Enable/Disable | 0 = Enabled (Default)<br>1 = Disabled | Used with WP# to enable or disable writing to the status register. This bit is writable.                                                                                                                 | Non-<br>volatile |   |

#### Notes

- 1. All BP bits must be set to 0 for the Bulk Erase command execution

- 2. Bit 0 is the inverse of Flag Status Register Bit 7

Table 6

#### Status Register Write Enable/Disable Bit [7]

This bit enables write protect for the Status register when set to '1' and the write protect (WP#) pin is driven LOW. In this mode, any instruction that changes the status register content is ignored, effectively locking the state of the device. If SR Bit [7] is set to '0', irrespective of the WP status (LOW or HIGH), status register write protection remains disabled. Refer to Table 7 for the memory and status register protection options.

#### Top/ Bottom Protection Bit [5]

This bit defines the operation of the Block Protection bits BP3, BP2, BP1, and BP0. This bit controls the starting point of the memory array (from top or bottom) that gets protected by the Block protection bits.

#### Block Protection (BP3, BP2, BP1 and BP0) [6,4:2]

These bits define the memory array to be write-protected against memory write commands. When one or more of the BP bits is set to '1', the respective memory address is protected from writes. The Block Protect bits (BP3, BP2, BP1, and BP0) in combination with the T/B bit can be used to protect an address or sector range of the memory array. The size of the range is determined by the value of the BP bits and the upper or lower starting point of the range which is selected by the T/B. Table xx shows EM128LX protected address range for BP[3:0] bits setting.

#### Write Enable Latch (WEL) Bit [1]

The WEL bit must be set to 1 to enable write operations to the memory array or registers, as shown in Table xx. This bit is set to '1' only by executing the Write Enable (WREN) command. The WEL bit (SR1[1]) automatically clears to '0' after a Write Disable (04h) command is executed. Write (Program) commands will not reset WEL at the completion of the command allowing for back-to-back writes to memory without loading the WREN command again. The WEL bit is volatile and returns to its default '0' state after POR, software RESET, and hardware RESET (via the RESET# pin when available).

#### 5.2 HARDWARE WRITE PROTECTION

Designated protected blocks as set by SR Bits [6:2], (BP3:0 and TB) are hardware protected with the WP# pin. When the enable/disable bit of the status register is set to 1 and the WP# signal is driven LOW, the status register nonvolatile bits become read-only and the Write Status Register command (01h) operation will not execute. During the extended-SPI protocol with Quad Output Fast Read, Quad IO Fast Read, Octal Output Fast Read, Octal IO Fast Read commands, and with Quad SPI and Octal SPI protocols, this pin function is an input/output with IO2 functionality. Table xx below explains how the Write Protection is enabled or disabled with the Status register write enable/disable bit 7, the WEL bit 1 and the WP# signal.

|     |     |      |       | _     |       |

|-----|-----|------|-------|-------|-------|

| Tak | J۵. | 7. I | Mrita | Prote | ction |

|     |     |      |       |       |       |

| SR Bit[7] | WP#  | WEL Bit [1] | Protected<br>Blocks | Unprotected<br>Blocks | Status Register |

|-----------|------|-------------|---------------------|-----------------------|-----------------|

| Х         | Χ    | 0           | Protected           | Protected             | Protected       |

| 0         | Χ    | 1           | Protected           | Writable              | Writable        |

| 1         | Low  | 1           | Protected           | Writable              | Protected       |

| 1         | High | 1           | Protected           | Writable              | Writable        |

Table 7

#### **Block Protection Settings**

Sectors can be protected from Program and Erase operations by setting the TB and BP[3:0] bits corresponding to those sectors as shown in Table 8. If the address of a Write(Program) command is within a protected area, the Write will not execute. Writing will not resume until a new write command is issued with an address in an unprotected area. In other words, a write operation will not skip over a protected area and resume in the next unprotected area. A new Write command is required once an ongoing write aborts

**Table 8: Block Protection- Protected Areas**

|            |     |     |     |     |         | Protector<br>for given | ed 64KB S<br>part dens |       |       |

|------------|-----|-----|-----|-----|---------|------------------------|------------------------|-------|-------|

| Top/Bottom | BP3 | BP2 | BP1 | BP0 | 128     | 64                     | 32                     | 16    | 8     |

| 0          | 0   | 0   | 0   | 0   | None    | None                   | None                   | None  | None  |

| 0          | 0   | 0   | 0   | 1   | 255:255 | 127:127                | 63:63                  | 31:31 | 15:15 |

| 0          | 0   | 0   | 1   | 0   | 255:254 | 127:126                | 63:62                  | 31:30 | 15:14 |

| 0          | 0   | 0   | 1   | 1   | 255:253 | 127:125                | 63:61                  | 31:29 | 15:13 |

| 0          | 0   | 1   | 0   | 0   | 255:252 | 127:124                | 63:60                  | 31:28 | 15:12 |

| 0          | 0   | 1   | 0   | 1   | 255:251 | 127:123                | 63:59                  | 31:27 | 15:11 |

| 0          | 0   | 1   | 1   | 0   | 255:250 | 127:122                | 63:58                  | 31:26 | 15:10 |

| 0          | 0   | 1   | 1   | 1   | 255:249 | 127:121                | 63:57                  | 31:25 | 15:9  |

| 0          | 1   | 0   | 0   | 0   | 255:248 | 127:120                | 63:56                  | 31:24 | 15:8  |

| 0          | 1   | 0   | 0   | 1   | 255:240 | 127:112                | 63:48                  | 31:16 | 15:0  |

| 0          | 1   | 0   | 1   | 0   | 255:224 | 127:96                 | 63:32                  | 31:0  | 15:0  |

| 0          | 1   | 0   | 1   | 1   | 255:192 | 127:64                 | 63:0                   | 31:0  | 15:0  |

| 0          | 1   | 1   | 0   | 0   | 255:128 | 127:0                  | 63:0                   | 31:0  | 15:0  |

| 0          | 1   | 1   | 0   | 1   | 255:0   | 127:0                  | 63:0                   | 31:0  | 15:0  |

| 0          | 1   | 1   | 1   | 0   | 255:0   | 127:0                  | 63:0                   | 31:0  | 15:0  |

| 0          | 1   | 1   | 1   | 1   | 255:0   | 127:0                  | 63:0                   | 31:0  | 15:0  |

| 1          | 0   | 0   | 0   | 0   | None    | None                   | None                   | None  | None  |

| 1          | 0   | 0   | 0   | 1   | 0:0     | 0:0                    | 0:0                    | 0:0   | 0:0   |

| 1          | 0   | 0   | 1   | 0   | 1:0     | 1:0                    | 1:0                    | 1:0   | 1:0   |

| 1          | 0   | 0   | 1   | 1   | 2:0     | 2:0                    | 2:0                    | 2:0   | 2:0   |

| 1          | 0   | 1   | 0   | 0   | 3:0     | 3:0                    | 3:0                    | 3:0   | 3:0   |

| 1 | 0 | 1 | 0 | 1 | 4:0   | 4:0   | 4:0  | 4:0  | 4:0  |

|---|---|---|---|---|-------|-------|------|------|------|

| 1 | 0 | 1 | 1 | 0 | 5:0   | 5:0   | 5:0  | 5:0  | 5:0  |

| 1 | 0 | 1 | 1 | 1 | 6:0   | 6:0   | 6:0  | 6:0  | 6:0  |

| 1 | 1 | 0 | 0 | 0 | 7:0   | 7:0   | 7:0  | 7:0  | 7:0  |

| 1 | 1 | 0 | 0 | 1 | 15:0  | 15:0  | 15:0 | 15:0 | 15:0 |

| 1 | 1 | 0 | 1 | 0 | 31:0  | 31:0  | 31:0 | 31:0 | 15:0 |

| 1 | 1 | 0 | 1 | 1 | 63:0  | 63:0  | 63:0 | 31:0 | 15:0 |

| 1 | 1 | 1 | 0 | 0 | 127:0 | 127:0 | 63:0 | 31:0 | 15:0 |

| 1 | 1 | 1 | 0 | 1 | 255:0 | 127:0 | 63:0 | 31:0 | 15:0 |

| 1 | 1 | 1 | 1 | 0 | 255:0 | 127:0 | 63:0 | 31:0 | 15:0 |

| 1 | 1 | 1 | 1 | 1 | 255:0 | 127:0 | 63:0 | 31:0 | 15:0 |

Table 8

### 5.3 FLAG STATUS REGISTER

The Read Flag Status Register command is used to read the Flag status register bits. Flag status registers bits are volatile and are reset to zero on power-up. They are set and reset automatically by the internal controller. Error bits must be cleared through the Clear Flag Status Register command. For Soft Reset, Hardware Reset and Reset with signal sequence, bits 1, 3, 4, and 5 are set to "0"; bit 7 is set to "1". In a Reset with signal sequence, bit 0 is set to "0".

|     |                             | Table 9: Flag                                  | Status Register                                                                                                                                                                                                      |        |

|-----|-----------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Bit | Name                        | Settings                                       | Description                                                                                                                                                                                                          | Туре   |

| 0   | Addressing                  | 0 = 3-byte addressing<br>1 = 4-byte addressing | Indicates whether 3-byte or 4-byte address mode is enabled.                                                                                                                                                          | Status |

| 1   | Protection                  | 0 = Clear<br>1 = Protection Error              | Indicates whether an Erase or Program operation has attempted to modify the protected array sector as configured by Block Protection, or whether a OTP Write operation has attempted to access the locked OTP space. | Error  |

| 2   | Reserved                    |                                                |                                                                                                                                                                                                                      |        |

| 3   | CRC                         | 0 = Clear<br>1 = Failure                       | Indicates that the Computed CRC did not match the user provided CRC Code.                                                                                                                                            | Error  |

| 4   | Write (Program)             | 0 = Clear<br>1 = Program Error                 | Indicates whether a Program operation has succeeded or failed. A PROGRAM or OTP Write operation will fail if WREN.                                                                                                   | Error  |

| 5   | Erase                       | 0 = Clear<br>1 = Erase Error                   | Indicates whether an Erase operation has succeeded or failed. An Erase operation will fail if WREN is not set.                                                                                                       | Error  |

| 6   | Reserved                    |                                                |                                                                                                                                                                                                                      |        |

| 7   | Write (Program) or<br>Erase | 0 = Busy<br>1 = Ready                          | Indicates whether one of the following command cycles is in progress: Write Status Register, Write Nonvolatile Configuration Register, Write (Program), Erase, or CRC Check.                                         | Status |

Table 9

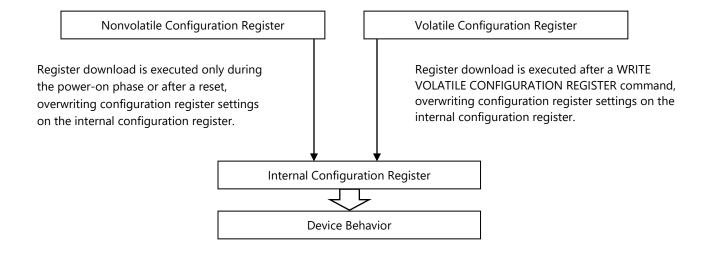

#### 5.4 Configuration Registers

The memory configuration is set by an internal configuration register that is not directly accessible to users. The user can change the default configuration at power up by using the WRITE NONVOLATILE CONFIGURATION REGISTER. Information from the nonvolatile configuration register overwrites the internal configuration register during power on or after a reset. The user can change the configuration during device operation using the WRITE VOLATILE CONFIGURATION REGISTER command. Information from the volatile configuration registers overwrite the internal configuration register immediately after the WRITE command completes. For stacked die product options, the configuration is replicated for each individual die in the stack. The user does not need to specify which die is being configured. The Write Nonvolatile Configuration or Write Volatile Configuration Register Commands will configure the entire stacked device for operation. Certain commands require that the die select register be written to select a given die. This is explained in Section 5.10, Die Select Register.

## 5.5 Nonvolatile configuration register

|                                  |                                 | ation Register 0                           |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|----------------------------------|---------------------------------|--------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Address                          | 0x000                           | 1                                          |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| Bit                              | Op                              | Name                                       | Settings                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Notes |

| 7:0                              | RW                              | I/O Mode                                   | 1111_1111 (0xFF)                                                      | SPI with DS (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6     |

|                                  |                                 |                                            | 1101_1111 (0xDF)                                                      | SPI w/o DS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                                  |                                 |                                            | 1111_1101 (0xFD)                                                      | Dual with DS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

|                                  |                                 |                                            | 1101_1101 (0xDD)<br>1111_1011 (0xFB)                                  | Dual w/o DS<br>Quad with DS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

|                                  |                                 |                                            | 1101_1011 (0xDB)                                                      | Quad w/o DS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

|                                  |                                 |                                            | 1110_1011 (0xEB)                                                      | Quad DTR with DS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

|                                  |                                 |                                            | 1100_1011 (0xCB)                                                      | Quad DTR w/o DS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|                                  |                                 |                                            | 1110_0111 (0xE7)                                                      | Octal DTR with DS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|                                  |                                 |                                            | 1100_0111 (0xC7)                                                      | Octal DTR w/o DS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |