#### Introduction

This user guide is provided to help users understand the Hardware and Software requirements needed for evaluation of the EMxxLX and EMxxLXB Industrial STT MRAM devices from Everspin.

This guide will outline the Hardware and Software requirements for the user to setup, configure, initialize, and generate traffic test vectors for the EMxxLX device.

This guide assumes the user has full access to the EMxxLX data sheet and a reasonable understanding of HW and SW usage. This guide makes references and links to other support documents for the user.

# Contents

| Introduction                                              | . 1 |

|-----------------------------------------------------------|-----|

| List of Figures and Tables                                | . 1 |

| 1. EMxxLX Daughter Card                                   | . 1 |

| 2. Required Host Board Support                            |     |

| 3. IDE (Integrated Development Environment) Support       |     |

| 4. Memory Controller Support                              | . 4 |

| 5. IDE Software Installation and Configuration            | . 4 |

| 6. Hardware connection, FPGA Image and .ELF file download | . 4 |

| Summary                                                   | . 5 |

| Revision History                                          | . 6 |

#### List of Figures and Tables

| Figure 1 EMxxLX Daughter Card                      | 2 |

|----------------------------------------------------|---|

| Figure 2 CRUVI CR00107-01                          |   |

| Figure 3 CRUVI CR00107-01 and EMxxLX Daughter Card | 5 |

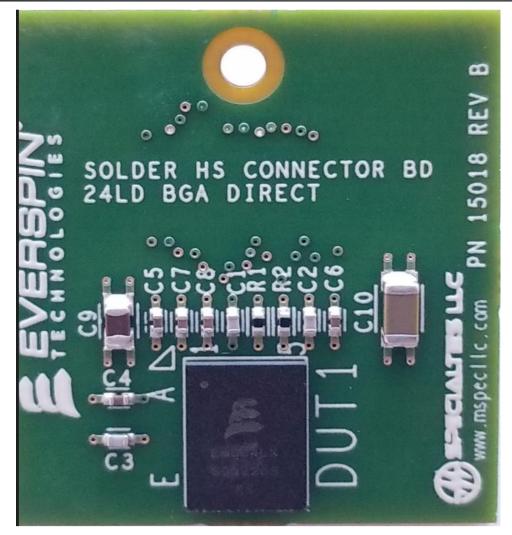

#### 1. EMxxLX Daughter Card

The EMxxLX Daughter Card is populated with Everspin EMxxLX 64Mbit Industrial STT MRAM device. Other EMxxLX densities can be populated as well. This device is obtained through the sample request form on Everspin's website located here: <u>https://www.everspin.com/info/request-serial-peripheral-interface-spi-evaluation-board</u>

1

FIGURE 1 EMxxLX DAUGHTER CARD

#### 2. Required Host Board Support

The EMxxLX evaluation board, here in referenced as the EMxxLX daughter card is designed to connect to the Open FPGA specification CRUVI CR00107-01 host board HS (High Speed) slot. This host platform is available to order from Trenz Electronic LLC website: <u>https://shop.trenz-electronic.de/en/CR00107-01-CRUVI-carrier-board-with-AMD-Spartan-7</u>

The CR00107-01 board has the following key features:

- SoC

- AMD Spartan-7

- RAM/Storage

- 8 MByte HyperRAM

- 16 or 32 MByte QSPI Flash

- On Board

- JTAG and UART over micro-USB connector

- 2 x User Push button

## November 2023 v1.1

- 2 x User LED

- Clock MEMS Oscillator 100MHz

- Interface

- o 1 x CRUVI LS

- 1 x CRUVI HS

- Power

- Power from micro-USB connector

- Dimension

- o 44.85 mm x 57.50 mm

#### FIGURE 2 CRUVI CR00107-01

# 3. IDE (Integrated Development Environment) Support

The AMD Spartan-7 FPGA is supported using the AMD Xilinx Vivado/Vitis IDE 2022.2 Software. The edition is a free use IDE and is available for download from AMD Xilinx web site located here: https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools/2022-2.html

3

Along with the IDE it is highly encouraged users download the AMD Xilinx recommended documentation from AMD Xilinx web site located here:

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/documentationnav/documentation-navigation-2022-2.html

## 4. Memory Controller Support

EMxxLX is Everspin's latest Industrial STT MRAM supporting JESD251 Expanded Serial Peripheral Interface (xSPI). To properly support this new JEDEC standard an xSPI compatible memory controller is required. Synaptic Labs LLC MBMC (Multi-Bus Memory Controller) IP is used in this evaluation board.

The Memory Controller IP temporary license (.lic) file is provided by Synaptic Labs LLC. Link for requesting temporary license file is here: <u>https://synaptic-labs.com/free-trial-request/</u>

After contacting and receiving the temporary license file, follow all directions contained in the Synaptic guide for installing and configuring the Memory controller IP.

## 5. IDE Software Installation and Configuration

To program the FPGA with the correct image, Vivado/Vitis IDE is used in conjunction with Synaptic Labs MBMC (Multi-Bus Memory Controller) IP. Locate the Vivado/Vitis IDE install file downloaded in section 3. Follow the installation instructions associated with the file. The user guide assumes default file location is used during the installation process.

#### 6. Hardware connection, FPGA Image and .ELF file download

To program the AMD Spartan-7 FPGA a Micro-USB cable with data connection is required. Ensure the cable supports data transfer and not just charging capabilities.

- Check Trenz CRUVI CR00107-01 documentation for information about schematics, jumpers, board

- configuration, etc.

- Make sure the STT-MRAM x8 CRUVI module is attached to Trenz CRUVI CR00107-01 board

- channel (J1)

- Connect CRUVI CR00107-01 board USB Port to and Host PC by USB cable

Figure 3 CRUVI CR00107-01 and EMxxLX Daughter Card

Open the AMD Xilinx Vitis IDE and follow sections 4.3-7.0 to create a memory test application and board support package for that Microblaze application.

#### Summary

This Evaluation platform user guide has been provided to give users the ability to evaluate Everspin's EMxxLX Industrial MRAM.

The detailed steps provide users with the required download and installation instructions for the Integrated Development Environment (IDE), SW support packages and License files. After proper configuration, the user can download the required FPGA .ELF files to test and evaluate EMxxLX industrial MRAM.

## **Revision History**

| Revision | Date               | Description of change                      |

|----------|--------------------|--------------------------------------------|

| 1.0      | September 28, 2023 | Initial Release                            |

| 1.1      | November 10, 2023  | Updated Memory Controller support section. |

|          |                    | Removed Reference Platform generation      |

|          |                    | section.                                   |

#

AMD (Xilinx) FPGA based EMxxLX Evaluation Platform User

#### **Contact Information:**

Author: Paolo Schiappacasse Name: EMEA Field Technical Specialist

#### How to Reach Us:

www.everspin.com

E-Mail:

support@everspin.com

orders@everspin.com

sales@everspin.com

#### USA/Canada/South and Central America

Everspin Technologies 5670 W. Chandler Road, Suite 100 Chandler, Arizona 85226 +1-877-347-MRAM (6726) +1-480-347-1111

#### Europe, Middle East and Africa

support.europe@everspin.com

#### Japan

support.japan@everspin.com

#### Asia Pacific

support.asia@everspin.com

# Everspin Technologies, Inc.

Information in this document is provided solely to enable system and software implementers to use Everspin Technologies products. There are no express or implied licenses granted hereunder to design or fabricate any integrated circuit or circuits based on the information in this document. Everspin Technologies reserves the right to make changes without further notice to any products herein. Everspin makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Everspin Technologies assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters, which may be provided in Everspin Technologies data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters including "Typical" must be validated for each customer application by customer's technical experts. Everspin Technologies does not convey any license under its patent rights nor the rights of others. Everspin Technologies products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Everspin Technologies product could create a situation where personal injury or death may occur. Should Buyer purchase or use Everspin Technologies products for any such unintended or unauthorized application, Buyer shall indemnify and hold Everspin Technologies and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Everspin Technologies was negligent regarding the design or manufacture of the part. Everspin<sup>™</sup> and the Everspin logo are trademarks of Everspin Technologies, Inc. All other product or service names are the property of their respective owners.

7