### Introduction

The EMxxLX family is the latest generation of MRAM devices based on Everspin's STT (Spin-transfer Torque) technology. It is a high performance, multiple I/O, SPI compatible MRAM device featuring a low pin count SPI bus interface with supported frequencies up to 200 Mhz. When the EMxxLX is configured for DTR operation with a clock speed of 200Mhz, transfer rates of 400MBps are achievable.

EMxxLX is designed as a 1.8V core and I/O signaling level device. If EMxxLX is being designed into systems without native 1.8V signaling, voltage level translation or Level Shifting is required.

A level shifter will take EMxxLX 1.8V I/O and shift it to the required Host controller I/O voltage. When designing in a level shifter certain considerations, such as providing appropriate voltages and level shifter timing impact must be accounted for.

# Contents

| Introduction                                   | 1 |

|------------------------------------------------|---|

| Level Shifter Voltage and Power Considerations | 1 |

| Level Shifter Timing Considerations            | 2 |

| Level Shifter Directional Control              | 3 |

| Conclusion                                     | 5 |

# Level Shifter Voltage and Power Considerations

When implementing a level shifter, the appropriate voltages for the Level Shifter and EMxxLX device must be considered.

A typical use case using EMxxLX 1.8V I/O in a 3.3V IO system will be examined. In this case the Level shifter will be Shifting the Master Device 3.3V I/O to Slave EMxxLX 1.8V I/O.

There are multiple level shifters from many different manufactures. The level shifter selection process is left to the system designer and beyond the scope of this document.

For example purposes, the Texas Instruments SN74ACV24T245 and LSF0102 were selected. Level shifting capabilities are rated from 1.2V-3.6V with maximum data rate of 380Mbs (1.8V to 3.3V Translation).

For proper level shifter functionality, it must be sourced with both 1.8V and 3.3V. It is assumed the Master controller requires 3.3V for I/O and has a 3.3V voltage plane. If possible, the source of 3.3V plane could be used to source the 3.3V requirements of the level shifter. If the platform has a 1.8V plane this may be used to source the 1.8V requirements of the level shifter.

Careful consideration must be used when using existing power sources to power the level shifter. The power requirements of the level shifter must not exceed the sourcing capabilities of the platforms power delivery network.

# Level Shifter Timing Considerations

All Level shifters have an inherent Propagation Delay (Pd) associated with the device. This delay is the time required to switch and level shift the input signal to the output. The propagation delay must be accounted for when selecting the appropriate level shifter.

As a rule of thumb, the smaller the propagation delay the better. The timing parameters to consider when selecting a level shifter are:

- A) Frequency or Clock Period of Master Controller

- B) Propagation delay of level shifter

- C) Set up and Hold time requirements of the Master and Slave.

For example, if the xSPI, QSPI or SPI bus is operating at 100Mhz the clock period is 10ns. If operating in DTR mode the period is 5ns, as data will be transferred on both the rising and falling edge of the clock or DS (Data Strobe) if supported.

When determining the impact of the Level Shifter propagation delay, subtract the level shifter propagation delay from the system timing window.

# Level Shifter Directional Control

Depending upon the level shifter selection/implementation, directional Control may or may not be required. Direction control is defined as the direction of data flow, either to or from the EMxxLX device.

If direction control is required, a dedicated logic pin on the Master controller is used to control the direction of data during Reads/Writes to the EMxxLX device.

If direction control pin is not available, follow the level shifter manufactures design guidelines for the proper implementation and connection scheme.

# **Typical Level Shifter Implementations**

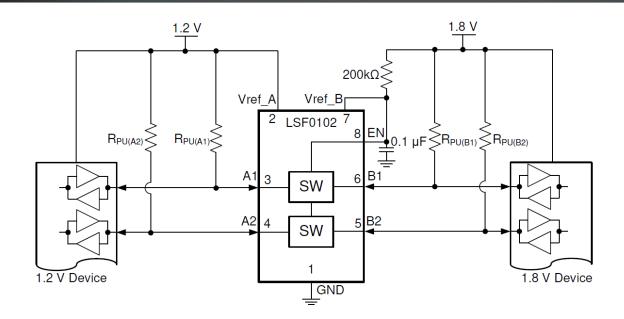

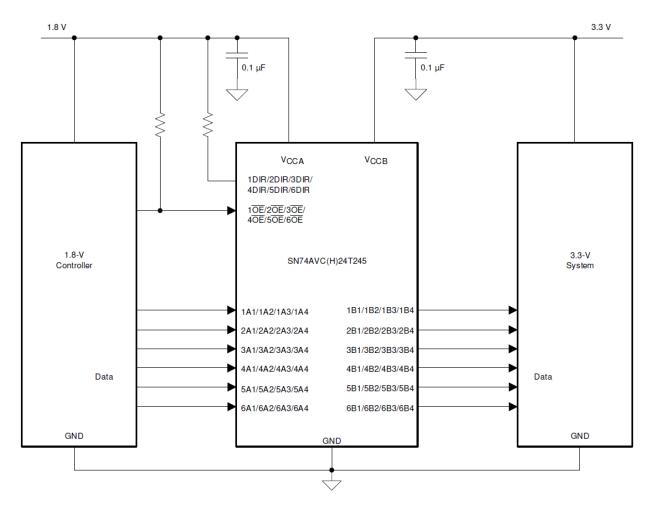

For illustrative purposes Figure 1 and Figure 2 depict two typical level shifter implementations using the TI LSF0102 and SN74AVC24T245. The depictions below are for example purposes only and may not depict the designer's specific implementation. Follow the manufactures recommended design guidelines to ensure the level shifter implementation meets the design criteria.

FIGURE 1 EXAMPLE LSF0102 LEVEL SHIFTER IMPLEMENTATION AUTOMATIC DIRECTION CONTROL

FIGURE 2 EXAMPLE SN74AVC24T245 LEVEL SHIFTER IMPLEMENTATION WITH DIRECTION CONTROL

# Conclusion

In certain designs where the Master controller's IO voltage is not 1.8V, a level shifter may be designed in to translate or shift the 1.8V to the desired logic level. Care must be taken to ensure proper voltages and timing impact of the level shifter are understood and accommodated for.

#### **Contact Information:**

Author: Daniel R. Symalla

Sr. FAE

WW Sales Group

### How to Reach Us:

www.everspin.com

E-Mail:

support@everspin.com

orders@everspin.com

sales@everspin.com

### USA/Canada/South and Central America

**Everspin Technologies**

5670 W. Chandler Road, Suite 100

Chandler, Arizona 85226

+1-877-347-MRAM (6726)

+1-480-347-1111

### Europe, Middle East and Africa

support.europe@everspin.com

#### Japan

support.japan@everspin.com

### Asia Pacific

support.asia@everspin.com

### Everspin Technologies, Inc.

Information in this document is provided solely to enable system and software implementers to use Everspin Technologies products. There are no express or implied licenses granted hereunder to design or fabricate any integrated circuit or circuits based on the information in this document. Everspin Technologies reserves the right to make changes without further notice to any products herein. Everspin makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Everspin Technologies assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters, which may be provided in Everspin Technologies data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters including "Typical" must be validated for each customer application by customer's technical experts. Everspin Technologies does not convey any license under its patent rights nor the rights of others. Everspin Technologies products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Everspin Technologies product could create a situation where personal injury or death may occur. Should Buyer purchase or use Everspin Technologies products for any such unintended or unauthorized application, Buyer shall indemnify and hold Everspin Technologies and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Everspin Technologies was negligent regarding the design or manufacture of the part. Everspin<sup>™</sup> and the Everspin logo are trademarks of Everspin Technologies, Inc. A 11 - L-