## Introduction

The EMxx64LX is the latest generation of MRAM devices based on Everspin's Industrial STT (Spin-Transfer Torque) technology. It is a high-performance, multiple I/O, SPI compatible MRAM device featuring a low pin count SPI bus interface with supported frequencies up to 200 Mhz. When the EMxx64LX is configured for DTR operation with a clock speed of 200Mhz, transfer rates of 400MBps are achievable.

The device state cannot be guaranteed after a solder reflow operation, hence a full device initialization and configuration is required. This document will outline the required steps, sequence of operations, and register settings required to have the EMxx64LX in a fully functional and ready state.

It is assumed the reader has full access to EMxx64LX data sheet as certain registers and functions of the device are referenced throughout this document.

# Contents

| Intro | oduction                                                                     | 1  |

|-------|------------------------------------------------------------------------------|----|

| List  | of Figures and Tables                                                        | 2  |

| 1.    | Device Initialization, Power Cycle, System Resets and Recovery logical flows | 2  |

| 2.    | SPI Interface configuration                                                  | 6  |

| 3.    | JEDEC Reset Considerations                                                   | 6  |

| 4.    | Nonvolatile Configuration Settings                                           | 7  |

| 5.    | Volatile Configuration Register Settings                                     | 7  |

| 6.    | Status Register                                                              | 9  |

| 7.    | Flag Status Register                                                         | 9  |

| 8.    | Interrupt Status Register                                                    | 10 |

| 9.    | OTP Considerations                                                           | 10 |

| 10.   | Configuration Save State and verification                                    | 10 |

| 11.   | Array Initialization Steps                                                   | 11 |

| 12.   | Device Initialization Command sequence                                       | 11 |

| 13.   | Undefined or Unexpected device operation                                     | 11 |

| Con   | clusion                                                                      | 12 |

| Revi  | ision History                                                                | 12 |

1

Device Initialization, Power Cycle, System Reset and Recovery for EMxxLX MRAM

# List of Figures and Tables

| Figure 1 Device Initialization Flow         | 3 |

|---------------------------------------------|---|

| Figure 2 Device Power On/Reset Flow         | 4 |

| Figure 3 Device Recovery Flow part 1        |   |

| Figure 4 Device Recovery Flow Part 2        |   |

| Figure 5 JESD252 Reset with Signal Sequence |   |

| Table 1 | Nonvolatile Configuration Registers | 7  |

|---------|-------------------------------------|----|

| Table 2 | Volatile Configuration Registers    | 8  |

| Table 3 | Flag Status Register                | 9  |

| Table 4 | Interrupt Flag and Status           | 10 |

# 1. Device Initialization, Power Cycle, System Resets and Recovery logical flows

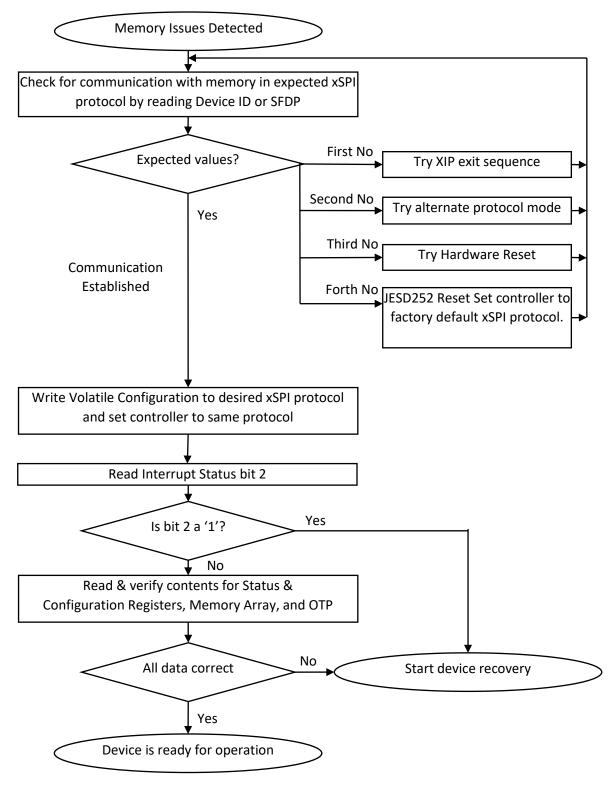

For device initialization, Power On/Reset and recovery an order of operations or 'logical flow' has been developed. This flow is designed to assist the user in defining the logical sequence and steps required for device initialization and recovery. The need for device recovery is considered a very low probability event but is included here for completeness. Determining when the recovery flow should be initiated or is required is left to the system designers. It is assumed some level of end-to-end data protection scheme will be implemented. This protection scheme will be the first to identify undefined or unexpected system behavior.

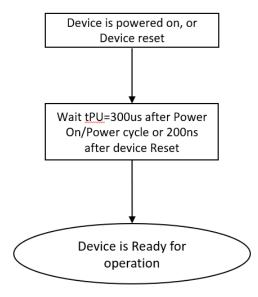

It is intended that host controllers follow the Device Initialization flow for first time power-on after device manufacturing. The Device Power On or Device Reset Flow will be used for subsequent power on or reset events.

Determining when the recovery process should be done is left to the system designers. General reasons to consider running the recovery process would be:

- Inability to communicate with the memory device.

- Which could come from loss of synchronization between the system memory controller and the memory via a reset or power lost to one but not the other device.

- Or a failure of power-on or other reset initialization of the memory xSPI logic.

- This communication failure may be detected by a system watchdog time out or by boot or diagnostic code, executing from a different system memory resource, that is used to verify data integrity of the memory contents before normal system operation begins.

- Detection of a Power-on error shown in the Flag Status Register bit 2 when set to 1.

- Detection of data errors in the non-volatile configuration registers, main memory array, or OTP memory array.

2

It is assumed some type of data integrity monitoring scheme will be implemented by the system, such as a checksum or CRC on the memory arrays. This protection scheme will likely be the first to identify memory content errors

Device Initialization, Power On/Reset and recovery flows are defined in Figures 1, 2 and 3 below.

3

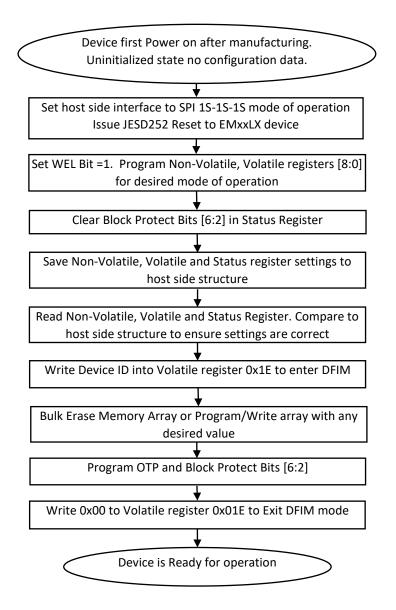

FIGURE 1 DEVICE INITIALIZATION FLOW

Device Initialization, Power Cycle, System Reset and Recovery for EMxxLX MRAM

FIGURE 2 DEVICE POWER ON/RESET FLOW

Device Initialization, Power Cycle, System Reset and Recovery for EMxxLX MRAM

FIGURE 3 DEVICE RECOVERY FLOW PART 1

# Device Initialization, Power Cycle, System Reset and Recovery for EMxxLX MRAM

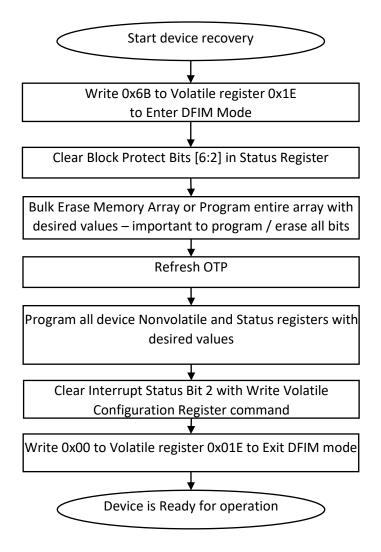

FIGURE 4 DEVICE RECOVERY FLOW PART 2

## 2. SPI Interface configuration

After manufacturing and reflow operations device register settings and array contents are not defined.

The EMxx64LX interface default configuration after a solder reflow operation or JEDEC reset is SPI 1S-1S-1S mode of operation. All initial commands must use this format until the interface is configured for desired mode of operation.

## 3. JEDEC Reset Considerations

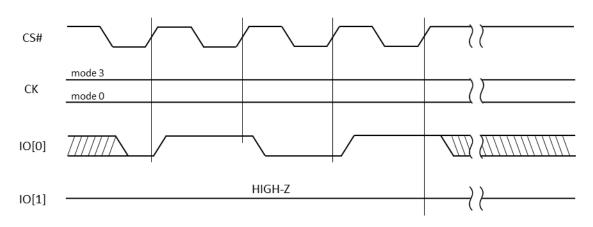

Not all MCU controllers natively support JESD252 Signal reset sequence. In this scenario it is recommended customers investigate the GPIO remapping capabilities of the MCU controller used in the design. In many modern MCU it is possible to remap the current SPI interface signals as GPIO. If possible, remap CS#, CK, IO 0:1 as GPIO signals. Using the logic control capabilities of the GPIO signals perform the Signal Reset sequence outlined in Figure 4.

Device Initialization, Power Cycle, System Reset and Recovery for EMxxLX MRAM

FIGURE 5 JESD252 RESET WITH SIGNAL SEQUENCE

#### 4. Nonvolatile Configuration Settings

EMxxLX Nonvolatile configuration registers are used to store the device configuration state. The Nonvolatile Configuration registers overwrite Internal Configuration Registers after Power-on or after a device reset. The user can change the default configuration at power up by using the Write Nonvolatile Configuration Register. Please refer to EMxx64LX product data sheet for full register description and bit definitions. A brief summary of the Nonvolatile configuration registers is provided below in Table 1.

| Nonvolatile Configuration<br>Register | Address   | Width | Functional Summary       |

|---------------------------------------|-----------|-------|--------------------------|

| Register 0                            | 0x00_0000 | 8 bit | I/O Mode settings        |

| Register 1                            | 0x00_0001 | 8 bit | Dummy Cycle              |

|                                       |           |       | Configuration            |

| Register 2                            | 0x00_0002 | 8 bit | Reserved                 |

| Register 3                            | 0x00_0003 | 8 bit | I/0 Driver Strength      |

| Register 4                            | 0x00_0004 | 8 bit | DS delay                 |

| Register 5                            | 0x00_0005 | 8 bit | Address Mode             |

| Register 6                            | 0x00_0006 | 8 bit | XIP Configuration        |

| Register 7                            | 0x00_0007 | 8 bit | Wrap Configuration       |

| Register 8                            | 0x00_0008 | 8 bit | Erase, Reset, Write mode |

TABLE 1 NONVOLATILE CONFIGURATION REGISTERS

## 5. Volatile Configuration Register Settings

Volatile configuration registers are used to overwrite the device configuration during operation or run time. Register download is executed after a Write Volatile Configuration Register Command. This command will overwrite configuration settings in Internal Configuration Registers.

| Nonvolatile Configuration<br>Register | Address   | Width | Functional Summary |

|---------------------------------------|-----------|-------|--------------------|

| Register 0                            | 0x00_0000 | 8 bit | I/O Mode settings  |

| Register 1                            | 0x00_0001 | 8 bit | Dummy Cycle        |

|                                       |           |       | Configuration      |

| Register 2                            | 0x00_0002 | 8 bit | Reserved           |

7

Device Initialization, Power Cycle, System

Reset and Recovery for EMxxLX MRAM

| Register 3 | 0x00_0003 | 8 bit | I/0 Driver Strength      |

|------------|-----------|-------|--------------------------|

| Register 4 | 0x00_0004 | 8 bit | DS delay                 |

| Register 5 | 0x00_0005 | 8 bit | Address Mode             |

| Register 6 | 0x00_0006 | 8 bit | XIP Configuration        |

| Register 7 | 0x00_0007 | 8 bit | Wrap Configuration       |

| Register 8 | 0x00_0008 | 8 bit | Erase, Reset, Write mode |

TABLE 2

VOLATILE CONFIGURATION REGISTERS

## 6. Status Register

Read Status Register or Write Status Register commands are used to read from or write to the Status Register bits, respectively. When the status register enable/disable bit (bit 7) is set to 1 and WP# is driven LOW, the status register nonvolatile bits become read-only and the Write Status Register operation will not execute. This hardware-protected mode is exited by driving WP# high.

For array initialization and recovery, the BP bits [6:2] must be cleared or set to '0'. This disables block protection and defines all areas of the array as writable.

# 7. Flag Status Register

The Read Flag Status Register command is used to read the Flag status register bits. Flag status registers bits are volatile and are reset to zero on power-up They are set and reset automatically by the internal controller. Error bits must be cleared through the Clear Status Register command.

| Flag Status Register |                                                                                                                                                                                                                                    |                                                 |                                                                                                                                                                                                                               |        |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|

| Bit                  | Name                                                                                                                                                                                                                               | Settings                                        | Description                                                                                                                                                                                                                   | Туре   |  |  |

| 0                    | Addressing                                                                                                                                                                                                                         | 0 = 3-byte addressing<br>1 = 4-byte addressing  | Indicates whether 3-byte or 4-byte address mode is enabled.                                                                                                                                                                   | Status |  |  |

| 1                    | Protection                                                                                                                                                                                                                         | 0 = Clear<br>1 = Failure or Protection<br>Error | Indicates whether an Erase or Program operation has<br>attempted to modify the protected array sector as<br>configured by Block Protection, or whether a OTP Write<br>operation has attempted to access the locked OTP space. | Error  |  |  |

| 2                    | Reserved                                                                                                                                                                                                                           |                                                 |                                                                                                                                                                                                                               |        |  |  |

| 3                    | 3 CRC 0 = Clear Indicates that the Computed CRC did not match the user provided CRC Code.                                                                                                                                          |                                                 | Error                                                                                                                                                                                                                         |        |  |  |

| 4                    | Write (Program)0 = ClearIndicates whether a Program operation has succeeded or<br>failed. A PROGRAM or OTP Write operation will fail if WREI<br>is not set or attempting to PROGRAM a region that has<br>Block Protection enabled. |                                                 | Error                                                                                                                                                                                                                         |        |  |  |

| 5                    | Erase                                                                                                                                                                                                                              | 0 = Clear<br>1 = Failure or Protection<br>Error | Indicates whether an Erase operation has succeeded or failed. An Erase operation will fail if WREN is not set.                                                                                                                | Error  |  |  |

| 6                    | Reserved                                                                                                                                                                                                                           |                                                 |                                                                                                                                                                                                                               |        |  |  |

| 7                    | Write (Program) or<br>Erase                                                                                                                                                                                                        | 0 = Busy<br>1 = Ready                           | Indicates whether one of the following command cycles is<br>in progress: Write Status Register, Write Nonvolatile<br>Configuration Register, Write (Program), Erase, or CRC<br>Check.                                         | Status |  |  |

9

TABLE 3

FLAG STATUS REGISTER

## 8. Interrupt Status Register

The Interrupt Mask and Status registers are used together to provide the status of certain operations or indicate errors in particular operations as shown in the tables below. The mask register provides the option to receive an interrupt signal on the INT# pin. The INT# is available on the 24-ball BGA, ball A5 but is not available on the 8-DFN package. Configuration errors, CRC completion and Erase completion are the operations that generate a status bit. The Interrupt registers are accessed with the Read Volatile Configuration Register and Write Volatile Configuration Register commands.

| Address | 0x00_000F |            |                                               |                                                                        |       |  |

|---------|-----------|------------|-----------------------------------------------|------------------------------------------------------------------------|-------|--|

| Bit     | Ор        | Name       | Settings                                      | Description                                                            | Notes |  |

| 7:2     | RO        | Reserved   | 0                                             |                                                                        |       |  |

| 1       | RW        | CRC Done   | 0 = Masked (default)<br>1 = Interrupt enabled | Enable interrupt on CRC Check Done                                     |       |  |

| 0       | RW        | Erase Done | 0 = Masked (default)<br>1 = Interrupt enabled | Enable interrupt on Erase Done<br>1=Masked - no interrupt is generated |       |  |

| Interrupt S | Interrupt Status |                |                                         |                                        |       |  |

|-------------|------------------|----------------|-----------------------------------------|----------------------------------------|-------|--|

| Address     | ss 0x00_0010     |                |                                         |                                        |       |  |

| Bit         | Ор               | Name           | Settings                                | Description                            | Notes |  |

| 7:3         | RO               | Reserved       | 0                                       |                                        |       |  |

| 2           | RW1C             | Power On Error | 0 = No error<br>1 = Error               | Read, Write 1 to Clear, Power on error | 1     |  |

| 1           | RW1C             | CRC Done       | 0 = Not done (Reset Value)<br>1 = Done  | Read, Write 1 to Clear                 |       |  |

| 0           | RW1C             | Erase Done     | 0 = Note done (Reset Value)<br>1 = Done | Read, Write 1 to Clear                 |       |  |

TABLE 4 INTERRUPT FLAG AND STATUS

Note 1. Bit 2 does not get reset with a hardware reset.

## 9. OTP Considerations

A dedicated area of 256 bytes outside of the memory array is provided to allow specific user information to be stored on a non-volatile basis. This area is controlled using the OTP control byte and Volatile Configuration register 8, bit 2. Please refer to EMxx64LX data sheet section 14 for OTP operation and Control Byte specifics and, Section 5.5 for Nonvolatile Configuration Register definitions.

#### 10. Configuration Save State and verification

After the device is configured for desired operation, it is recommended to save all Volatile, Nonvolatile and Status Registers to a host side structure. This structure will be used for comparison during the Initialization and Recovery flow to ensure accuracy of device initialization.

## 11. Array Initialization Steps

For proper functional operation of the EMxx64LX, a memory Array initialization is required. This section defines the steps to properly initialize and program the memory array.

- 1) Set host side interface to SPI mode of operation.

- 2) Set WEL Bit=1.

- 3) Program Volatile and Non-Volatile configuration registers [8:0] for desired mode of operation.

- 4) Clear Block Protect bits [6:2] in device status register.

- 5) Save Volatile, Nonvolatile and Status registers settings to host side structure.

- 6) Read back Volatile, Nonvolatile and Status registers. Compare to host side structure to ensure setting are correct.

- 7) Write Device ID to Volatile register 0x1E to enter DFIM (Device Factory Initialization Mode)

- 8) Use Bulk Erase command or Program/Write to array with any desired value.

- 9) Reprogram OTP and Block Protect Bits [6:2].

- 10) Write 0x00 to Volatile register 0x1E to exit DFIM mode.

- 11) Device is ready for operation.

#### 12. Device Initialization Command sequence

To assist developers in generating the code sequence for device initialization a sample command sequence has been developed below. Please refer to proper timing and data sequence diagrams in EMxx64LX data sheet for details.

- 1) Set host controller to SPI mode. Please refer to documentation provided for the host controller.

- 2) Set WEL (Write Enable Latch) Bit 1

- a. Command = 06h

- 3) Write Non-Volatile and Volatile Registers

- a. Command = B1h/81H, Register Address, Register Data In

- 4) Save All Register Configurations to Host (Command Sequence is Host specific)

- 5) Read Non-Volatile, Volatile and Status Registers

- a. Command = 85h/B5h, Register Address, Dummy Cycles, Register Data

- 6) Write Device ID in Volatile register 0x1E to enter DFIM

- a. Command = 81h, Register Address, Register Data In

- 7) Bulk Erase Array

- a. Command = C7h/60h, Address

- 8) Program OTP and Set BP bits

- a. Write OTP Command = 42h, Address, Data

- b. Status Register Write Command = 01h, BP bits [6],[4:2] Top/Bottom bit [5]

- 9) Write 0x00 to Volatile register 0x1E to exit DFIM mode

- a. Command = 81h, Address = 0x1Eh, Register data = 0x00h

- 10) Device is ready for operation.

## 13. Undefined or Unexpected device operation

In the very rare and unlikely event of device corruption the device operation can become undefined. The probability of this event is deemed extremely rare. Host side data integrity schemes are expected to alert the system when this event occurs. If this event is detected refer to device recovery flow.

# Conclusion

Everspin's latest generation of STT MRAM device EMx64LX offers design flexibility and speed with its latest xSPI implementation. To ensure proper device operation after manufacturing and solder reflow, the device must be properly initialized. Following the sequence and steps outlined in this document will ensure the device operates in accordance with the specification outlined in the product data sheet.

#### **Revision History**

| Revision | Date            | Description of change                                          |

|----------|-----------------|----------------------------------------------------------------|

| 1.0      | April 7, 2022   | Initial Release                                                |

| 1.1      | June 8, 2022    | Added state to recovery flow to clear interrupt status bit [2] |

|          |                 | Added new section: Device Initialization Command sequence      |

| 1.2      | August 1, 2022  | Updated Device recovery flow                                   |

| 1.3      | August 24, 2022 | Added JEDEC Reset Considerations section                       |

|          |                 | Update Device Recovery flows                                   |

| 1.4      | Oct 5, 2022     | Added JESD252 Reset to Initialization Flow                     |

|          |                 | Updated device naming convention to EMxxLX                     |

| 1.5      | March 5, 2023   | Updated Command sequence step with Write Enable (06h)          |

#### **Contact Information:**

Author: Daniel Symalla

Senior FAE

WW Sales Group

#### How to Reach Us:

www.everspin.com

E-Mail:

support@everspin.com

orders@everspin.com

sales@everspin.com

#### **USA/Canada/South and Central America**

**Everspin Technologies**

5670 W. Chandler Road, Suite 100

Chandler, Arizona 85226

+1-877-347-MRAM (6726)

+1-480-347-1111

#### Europe, Middle East and Africa

support.europe@everspin.com

#### Japan

support.japan@everspin.com

#### Asia Pacific

support.asia@everspin.com

#### Everspin Technologies, Inc.

Information in this document is provided solely to enable system and software implementers to use Everspin Technologies products. There are no express or implied licenses granted hereunder to design or fabricate any integrated circuit or circuits based on the information in this document. Everspin Technologies reserves the right to make changes without further notice to any products herein. Everspin makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Everspin Technologies assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters, which may be provided in Everspin Technologies data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters including "Typical" must be validated for each customer application by customer's technical experts. Everspin Technologies does not convey any license under its patent rights nor the rights of others. Everspin Technologies products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Everspin Technologies product could create a situation where personal injury or death may occur. Should Buyer purchase or use Everspin Technologies products for any such unintended or unauthorized application, Buyer shall indemnify and hold Everspin Technologies and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Everspin Technologies was negligent regarding the design or manufacture of the part. Everspin<sup>™</sup> and the Everspin logo are trademarks of Everspin Technologies, Inc. All other product or service names are the property of their respective owners.

Copyright © 2022 Everspin Technologies, Inc.

EST 3000 Revision 1.5 March 2023