# Replacing the Fujitsu MB85RS4MTY SPI-FRAM with Everspin MR2xH40xDF SPI MRAM

#### **EVERSPIN MRAM MEMORY**

Everspin is the worldwide leader in designing, manufacturing, and commercially shipping discrete Magnetoresistive RAM (MRAM) into markets and applications where data persistence and integrity, low latency, and security are paramount. The MR2xH40xDF is a family of 4,194,304-bit magnetoresistive random access memory (MRAM) devices organized as 524,288 words of 8 bits. They are the ideal memory solution for applications that must store and retrieve data and programs quickly using a small number of I/O pins. They have serial EEPROM and serial Flash compatible read/write timing with no write delays and unlimited read/write endurance. Unlike other serial memories, with the MR2xH40xDF family both reads and writes can occur randomly in memory with no delay between writes.

### **OVERVIEW**

The MR2xH40xDF family is a SPI interface MRAM family with a memory array logically organized as 512Kx8 using the four pin interface of chip select (CS\), serial input (SI), serial output (SO) and serial clock (SCK) of the serial peripheral interface (SPI) bus. The MRAM implements a subset of commands common to SPI EEPROM and SPI Flash components. This allows the SPI MRAM to replace these components in the same socket and interoperate on a shared SPI bus. The SPI MRAM offers superior write speed, unlimited endurance, low standby & operating power, and simple, reliable data retention compared to other serial memory alternatives.

## **RELIABLE SUPPLY**

Everspin is a long term, reliable manufacturer of MRAM products and operates a fabrication facility in Chandler, Arizona.

### BENEFITS OF MR2xH40xDF

Upgrading to Everspin MRAM provides many benefits over Fujitsu FRAM:

- Faster Random Access Operation Times (50MHz/20ns tCLK and 40MHz/25ns tCLK)

- High Reliability and Data Retention (greater than 20 years at 125C Operating Temperature)

- Unlimited Read/Write Endurance

- No Wear-out Concern

- Automatic Data Protection On Power Loss

- Competitive Pricing

- Stable Manufacturing Supply Chain

## **COMMON PINS**

The MR2xH40xDF is a 4Mb non-volatile RAM organized 512Kx8 operating from a nominal 3.3V power supply and is compatible with FRAM. It is available in a standard 8-pin Small Flag DFN (DF version) and 8-pin DFN (DC version), which are versatile package options to make it a drop-in replacement with SPI-FRAM 8-pin plastic SOP and 8-pin DFN packages (Table 1).

Table 1. Pin and Package Comparison

| Feature/Function            | SPI MRAM (MR2xH40)                                              | SPI F-RAM (MB85RS4MTYY)                                                                                                              | Comments                                                                                                                                                                                                                                                                                                                          |

|-----------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8-pin DFN Exposed Metal PAD | Do not connect anything except VSS                              | It is allowed for the DIE PAD on the bottom of the DFN8 package to be floating (no connection to anything) or to be connected to VSS | The Exposed Metal Pad of the MRAM 8-pin DFN package is an NC (No Connect) pad; therefore, it can be either floating or connected to VSS. Everspin does not recommend soldering the MRAM DFN Exposed Metal Pad on the PCB                                                                                                          |

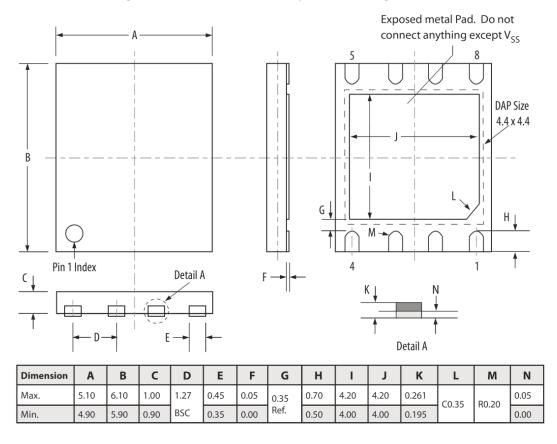

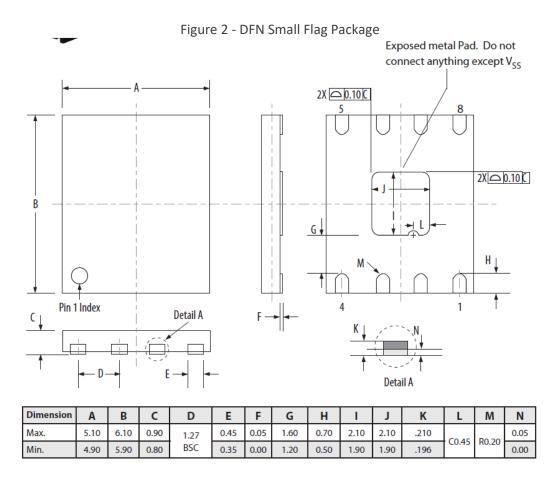

| 8-pin packages              | 8-pin DFN (MR2xH40xDC<br>8-pin DFN (Small Flag)<br>(MR2xH40xDF) | 8-pin plastic SOP                                                                                                                    | Both the 8-pin DFN packages of MRAM as shown in Figure 1 and Figure 2 are pin compatible and fit the Fujitsu 8-pin SOIC and DFN packages. They can be placed on a standard SOIC footprint in most designs. See also Application Note "EST01253 Everspin's New 2mm Exposed Pad DFN Package Meets Both SOIC-8 and DFN8 PCB Layouts" |

Figure 1 – 4 Mbit SPI MRAM 8-pin DFN Package Outline

The DC package option (8-DFN) is not recommended for new designs. Please select the DF (8-DFN small flag) option for new designs.

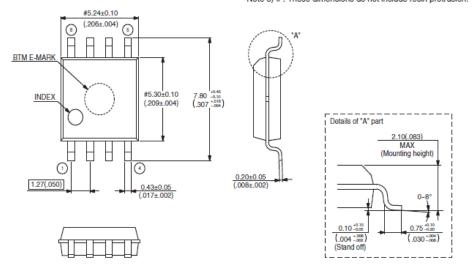

Figure 3 – 4 Mbit SPI FRAM 8-pin SOP (5.30 mm × 5.24 mm × 2.10 mm) Package Outline

8-pin plastic SOP (FPT-8P-M08) Note 1) Pins width and pins thickness include plating thickness. Note 2) Pins width do not include tie bar cutting remainder. Note 3) #: These dimensions do not include resin protrusion.

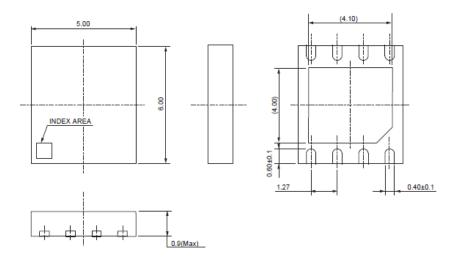

Figure 3 – 4 Mbit SPI FRAM 8-pin DFN (5 mm × 6 mm × 0.9 mm) Package Outline

The SPI MRAM Exposed Metal Pad is not connected to the die, hence it should be left floating or connected to Vss. Ensure that the Exposed Metal Pad of the SPI MRAM DFN and Small Flag DFN package is not soldered on the PCB when migrating from SPI FRAM. Doing so will cause the SPI MRAM die to be exposed to excessive heat, which could result in bit failures and margin loss.

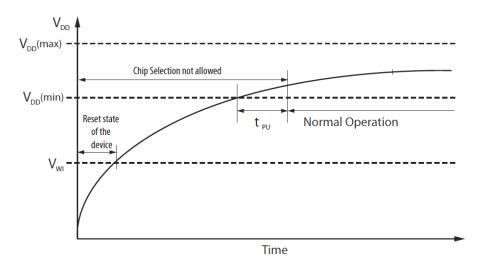

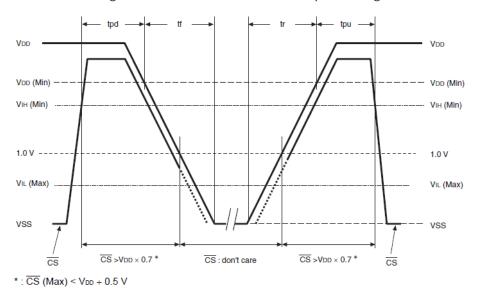

## POWER CYCLE TIMING

| Timing Parameters | Description                                | SPI MRAM (MR2xH40) | SPI FRAM<br>(MB85RS4MTYY) | Comments                                                                                                                              |

|-------------------|--------------------------------------------|--------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| tDP               | Sleep mode entry time                      | 3 μs               | Not applicable            | The SPI FRAM enters sleep as soon as CS\ toggles LOW to HIGH after the SLEEP command is entered                                       |

| tPU               | Power-up VDD(min) to first access (CS LOW) | 400 μs             | 450 μs                    | Systems must review the impact of different tpu time in the MRAM and adjust their timing accordingly                                  |

| tRDP (tREC)       | Recovery time from sleep                   | tRDP = 400 μs      | tRECHIB = 450 μs          | Systems must review the impact of different recovery time in the MRAM and adjust their timing accordingly                             |

| tDIS (tOD)        | Output disable time                        | tDIS = 12 ns (min) | tOD = 10 ns (max)         |                                                                                                                                       |

| tWPS (tCSU)       | WP Setup To CS Low                         | tWPS = 5 ns (min)  | tCSU = 5 ns (min)         |                                                                                                                                       |

| tWPH (tCSH)       | WP Hold From CS High                       | tWPH = 5 ns (min)  | tCSH = 5 ns (min)         |                                                                                                                                       |

| Power Parameters  | Description                                | SPI MRAM (MR2xH40) | SPI FRAM (MB85RS4MTY)     | Comments                                                                                                                              |

| IOUT              | DC output current per pin                  | ±20 mA             | Not specified             | This is the absolute maximum rating for the device. This parameter does not influence any device operation across its operating range |

| VWI               | Write inhibit voltage                      | 2.2 V              | Not applicable            | As soon as VDD falls below<br>VDD min limit, the SPI MRAM<br>writes are inhibited                                                     |

| tVR               | VDD power-up ramp rate                     | Not specified      | 50 μs/V                   | Systems must ensure that VDD power-up ramp rate is within the datasheet spec                                                          |

| tVF               | VDD power-down ramp<br>rate                | Not specified      | 100 μs/V                  | Systems must ensure that VDD power-down ramp rate is within the datasheet spec                                                        |

Figure 3 – 4 Mbit SPI MRAM Power Cycle Timing

Figure 4 – 4 Mbit SPI FRAM Power Cycle Timing

## Command (OPCODE) Compatibility

| Command OPCODE (Hex) | Command<br>Description | SPI MRAM<br>(MR2xH40xDF) | SPI FRAM<br>(MB85RS4MTY) | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|------------------------|--------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WREN (06h)           | Write Enable           | ٧                        | ٧                        | Identical functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| WRDI (04h)           | Write Disable          | ٧                        | ٧                        | Identical functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RDSR (05h)           | Read Status Register   | V                        | V                        | An RDSR command cannot immediately follow a READ command. If an RDSR command immediately follows a READ command, the output data will not be correct. Any other sequence of commands is allowed. If an RDSR command is required immediately following a READ command, it is necessary that another command be inserted before the RDSR is executed. Alternatively, two successive RDSR commands can be issued following the READ command. The second RDSR will output the proper state of the Status Register |

| WRSR (01h)           | Write Status Register  | ٧                        | ٧                        | Identical functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| READ (03h)           | Read Data Bytes        | ٧                        | ٧                        | Identical functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FSTRD (OBh)          | Fast read memory data  | Х                        | ٧                        | The 4-Mbit SPI MRAM doesn't support this command                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| WRITE (02h) | Write Data Bytes         | ٧ | ٧ | Identical functionality                                                                                                                                                                                                                  |  |

|-------------|--------------------------|---|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SLEEP (B9h) | Enter sleep mode         | ٧ | ٧ | The 4-Mbit SPI MRAM takes top (3 μs) to enter sleep                                                                                                                                                                                      |  |

| WAKE (ABh)  | Exit sleep mode          | √ | X | The 4-Mbit SPI FRAM does not support this command. Migrating from MRAM to FRAM does not require any software update because the SFRAM wakes up when CS toggles HIGH to LOW and ignores the subsequent WAKE instruction sent on its input |  |

| RDID (9Fh)  | Read device ID           | Χ | ٧ | The 4-Mbit SPI MRAM does not support this feature                                                                                                                                                                                        |  |

| DPD         | Deep Power Down          | Χ | ٧ | The 4-Mbit SPI MRAM does not support this feature                                                                                                                                                                                        |  |

| HIBERNATE   | Hibernate Mode           | Χ | ٧ | The 4-Mbit SPI MRAM does not support this feature                                                                                                                                                                                        |  |

| RUID        | Read Unique ID           | Χ | √ | The 4-Mbit SPI MRAM does not support this feature                                                                                                                                                                                        |  |

| WRSN        | Write Serial Number      | Χ | ٧ | The 4-Mbit SPI MRAM does not support this feature                                                                                                                                                                                        |  |

| RDSN        | Read Serial Number       | Χ | √ | The 4-Mbit SPI MRAM does not support this feature                                                                                                                                                                                        |  |

| SSWR        | Write Special Sector     | Χ | ٧ | The 4-Mbit SPI MRAM does not support this feature                                                                                                                                                                                        |  |

| SSRD        | Read Special Sector      | X | ٧ | The 4-Mbit SPI MRAM does not support this feature                                                                                                                                                                                        |  |

| FSSRD       | Fast Read Special Sector | Χ | ٧ | The 4-Mbit SPI MRAM does not support this feature                                                                                                                                                                                        |  |

| RFU         | Reserved                 | Χ | ٧ | The 4-Mbit SPI MRAM does not support this feature                                                                                                                                                                                        |  |

## Status Register Compatibility

The Status Register access in the case of the 4-Mbit SPI MRAM and the SPI FRAM are identical. However, the value returned by the Status Register read can differ between the two parts for some bit locations. For example, the "Don't Care" bits in the SPI MRAM Status Register are writeable and they can return either '0' or '1', while the "Don't Care" bits in the SPI F-RAM Status Register are read-only bits and always return '0'. Table below shows the Status Register bits definition for the two parts and their compatibilities.

| Status Register | SPI MRAM<br>(MR2xH40xDF) | SPI F-RAM<br>(MB85RS4MTY) | Comments                                                                                                                 |

|-----------------|--------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Bit0            | Don't Care               | Don't Care (0)            | This bit is non-writeable in the SPI FRAM and always returns '0' upon read. This bit can be modified in the SPI MRAM     |

| Bit1            | WEL                      | WEL                       | Identical behavior                                                                                                       |

| Bit2            | BP0                      | BP0                       | Identical behavior (Block Protect)                                                                                       |

| Bit3            | BP1                      | BP1                       | Identical behavior (Block Protect)                                                                                       |

| Bit4            | Don't Care               | Don't Care (0)            | These bits are read-only in the SPI FRAM and always return '0' upon read. These                                          |

| Bit5            | Don't Care               | Don't Care (0)            | bits can be modified in the SPI MRAM                                                                                     |

| Bit6            | Don't Care               | Don't Care (1)            | This bit is the read-only bit in the SPI FRAM and always returns '1' upon read. This bit can be modified in the SPI MRAM |

| Bit7            | SRWD                     | WPEN                      | Identical behavior                                                                                                       |

## **Device Spec Compatibility**

Everspin device is a 40 MHz/50MHz MRAM that operates at 2.7V - 3.6V, with a nominal Vdd = 3.3V, while the SPI-FRAM has a wider operating voltage range (1.8V to 3.6V). There are a few parameters that warrant some system level analysis before replacing the SPI-FRAM with the SPI-MRAM, including output load, start-up time and power up and power down ramps.

## RELIABILITY CONSIDERATIONS FOR COMPARISON

The MB85RS4MTY FRAM architecture employs ferroelectric materials as storage devices. These materials have an intrinsic electric dipole switched into opposite polarities with an external electric field. A read operation in a FRAM is destructive because it requires switching the polarization state in order to sense its state. The read operation has to restore the polarization to its original state after the initial read which adds cycle time to the read operation. FRAM Read and Write cycles require an initial "Pre-charge" time which can increase the initial access time. Ambient operating temperatures above 85°C accelerate wear-out of FRAM due to build-up of free electric charge resulting in imprint and also impact the 10 years data retention.

Everspin MRAM will provide the most cost-effective non-volatile RAM solution. MR2xH40xDF MRAM is built using a much simpler 1-transistor, 1-magnetic tunnel junction cell. The simple Everspin MRAM cell leads to improved

manufacturing efficiency and increased reliability. MRAM uses magnetic tunnel junction technology for non-volatile storage. Data does not leak away at high temperature and there is no wear-out mechanism to limit the number of read, write, or power cycles in this technology. Another important aspect of the reliability of toggle MRAM is the data retention against errors from thermally induced magnetization flips. Accelerated baking tests were conducted in which checkerboard patterns were written into the parts before the bake and the data was read back afterwards. The 1500 representative 4-Mb parts across three lots were baked under conditions ranging from 2000 h at 150 C to 2 h at 260 C and zero data retention flips were observed for all the parts. Extrapolation back to operating temperatures indicates a data retention lifetime exceeding 20 years. MRAM also offers radiation-hard performance due to the inherent robustness of the magnetic materials to radiation exposure. Alpha particle and neutron irradiation of 4-Mb dies showed an error rate of <0.5 FIT/Mb.

### MRAM MAGNETIC TOLERANCE

Everspin Technologies SPI MRAMs provide low susceptibility to data corruption when operated in magnetic field environments, therefore helping engineers to design high magnetic tolerance reliable systems. The maximum external magnetic field that can be applied to SPI MRAMs is 12000 A/m (150 Gauss), during write, read and standby operations. Everspin Technologies provide specific guides about how to operate MRAMs in these situations.

### **SUMMARY**

Replacing a MB85RS4MTY with Everspin's MR2xH40xDF 4Mb SPI MRAM is a straight-forward process. These devices are a drop-in replacement with some considerations of power supply and timing details shown in this application note. Everspin MRAM is also available with AEC-Q100 grade option with a data retention greater than 20 years, compared to the Fujitsu MRAM, which offers only 0.85 years of data retention at +125C, without any automotive qualification.

| Speed<br>Grade | Temp Grade       | Tempera-<br>ture | Package             | Shipping Container | Order Part Number        |

|----------------|------------------|------------------|---------------------|--------------------|--------------------------|

| 50MHz Ind      | Industrial       | -40 to +85 C     | 8-DFN Small<br>Flag | Trays              | MR20H40CDF               |

|                | maustriai        |                  |                     | Tape and Reel      | MR20H40CDFR              |

| 40 MHz         | Industrial       | -40 to +85 C     | 8-DFN <sup>1</sup>  | Trays              | MR25H40CDC <sup>1</sup>  |

|                |                  |                  |                     | Tape and Reel      | MR25H40CDCR <sup>1</sup> |

|                |                  |                  | 8-DFN Small<br>Flag | Trays              | MR25H40CDF               |

|                |                  |                  |                     | Tape and Reel      | MR25H40CDFR              |

|                | Extended         | -40 to +105 C    | 8-DFN Small<br>Flag | Trays              | MR25H40VDF               |

|                |                  |                  |                     | Tape and Reel      | MR25H40VDFR              |

|                | AEC-Q100 Grade 1 | -40 to +125 C    | 8-DFN Small<br>Flag | Trays              | MR25H40MDF               |

|                |                  |                  |                     | Tape and Reel      | MR25H40MDFR              |

Table 2 – Everspin MRAM Ordering Part Numbers

#### **Contact Information:**

Author:

Paolo Schiappacasse

**FAE EMEA**

**Everspin Sales**

### **How to Reach Us:**

www.everspin.com

E-Mail:

support@everspin.com

orders@everspin.com

sales@everspin.com

### **USA/Canada/South and Central America**

**Everspin Technologies**

5670 W. Chandler Road, Suite 100

Chandler, Arizona 85226

+1-877-347-MRAM (6726)

+1-480-347-1111

### **Europe, Middle East and Africa**

support.europe@everspin.com

### Japan

support.japan@everspin.com

#### **Asia Pacific**

support.asia@everspin.com

## Everspin Technologies, Inc.

Information in this document is provided solely to enable system and software implementers to use Everspin Technologies products. There are no express or implied licenses granted hereunder to design or fabricate any integrated circuit or circuits based on the information in this document. Everspin Technologies reserves the right to make changes without further notice to any products herein. Everspin makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Everspin Technologies assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters, which may be provided in Everspin Technologies data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters including "Typical" must be validated for each customer application by customer's technical experts. Everspin Technologies does not convey any license under its patent rights nor the rights of others. Everspin Technologies products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Everspin Technologies product could create a situation where personal injury or death may occur. Should Buyer purchase or use Everspin Technologies products for any such unintended or unauthorized application, Buyer shall indemnify and hold Everspin Technologies and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Everspin Technologies was negligent regarding the design or manufacture of the part. Everspin™ and the Everspin logo are trademarks of Everspin Technologies, Inc. All other product or service names are the property of their respective owners.