## Replacing the Cypress CY62136FV30LL MoBL SRAM with Everspin's MR1A16Axxx35 MRAM

#### **EVERSPIN MRAM MEMORY**

Everspin is the worldwide leader in designing, manufacturing, and commercially shipping discrete Magnetoresistive RAM (MRAM) into markets and applications where data persistence and integrity, low latency, and security are paramount.

### **RELIABLE SUPPLY**

Everspin is a long term, reliable manufacturer of MRAM products and operates a fabrication facility in Chandler, Arizona.

#### **OVERVIEW**

The Everspin 2Mb MRAM M1A16Axxx35 can operate with the Cypress 2Mb SRAM CY62136FV30LL slower timing, but also allows the system designer to take advantage of MRAM's faster random access cycle time. The Everspin 2Mb MRAM M1A16Axxx35 is available in 44 Pin TSOP2 as well as 48 Pin BGA packages.

#### **BENEFITS OF MR1A16Axxx35**

Upgrading to Everspin MRAM provides many benefits over Cypress SRAM:

- Faster Random Access Operation Times

- High Reliability and Data Retention

- Unlimited Read/Write Endurance

- No Wear-out Concern

- Competitive Pricing

- Stable Manufacturing Supply Chain

- Standard TSOP2 and BGA package

### GENERAL CONSIDERATIONS FOR REPLACING SRAM WITH MRAM

Everspin's Toggle MRAM (Magnetoresistive RAM) performs essentially as non-volatile SRAM. Replacing SRAM with MRAM in any application adds non-volatility without compromise of performance or function. Replacing a volatile SRAM with MRAM will provide instant 20-year data retention without the overhead of storing data to a non-volatile cell or the expense and space of a battery backup power source.

CONSIDERATIONS FOR REPLACING CYPRESS CY62136FV30LL (128k x 16) MoBL SRAM with EVERSPIN MR1A16Axxx35 (128k x 16) MRAM

Designers considering a replacement of CY62136FV30LL with MR1A16Axxx need to consider differences in package size and timing.

Table 1 - Overview: CY62136FV30LL-45ZSXI vs. MR1A16ACYS35

| Parameter          | CY62136FV30LL                  | MR1A16ACYS35              |  |

|--------------------|--------------------------------|---------------------------|--|

| Package            | 44 PIN TSOP2                   | 44 PIN TSOP2              |  |

| Size and Height    | 10.2 × 18.5 × 1.2 mm           | 10.2 x 18.5 x 1.2 mm      |  |

| Pinout / Footprint | See Figure 1 and Table 2 below |                           |  |

| Solder Profile     | Per JEDEC J-STD-020D.1         |                           |  |

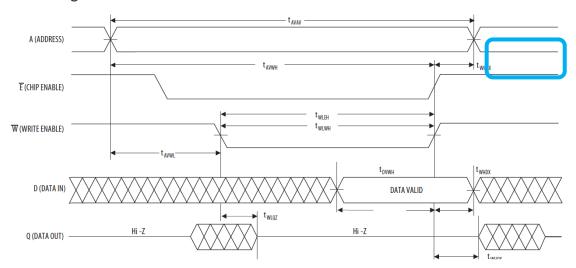

| Firmware / Timing  | Ons Address Hold Time          | 12ns Minimum Address Hold |  |

|                    |                                | Time. See Figure 7 below  |  |

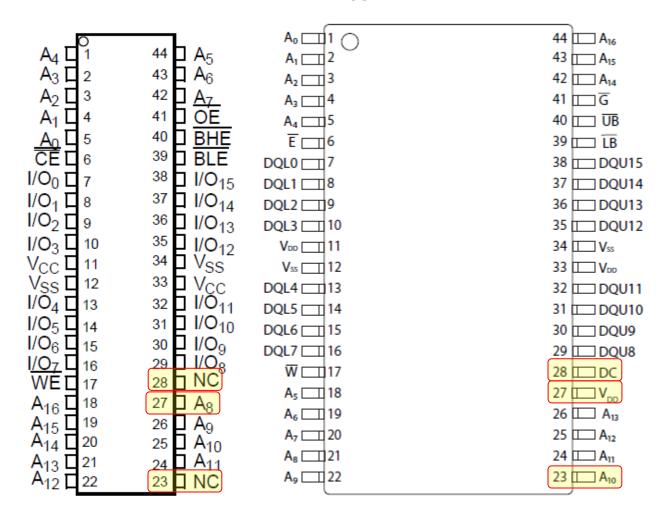

Figure 1 – Pinout/Footprint Comparison and Considerations

### 44 PIN TSOP2

**Cypress**

**Everspin Technologies**

Table 2 - Pin Function Comparison

| Pin # | Cypress | Everspin | <b>Everspin Definition</b> | Everspin Comments                                                                             |

|-------|---------|----------|----------------------------|-----------------------------------------------------------------------------------------------|

| 23    | NC      | A10      | Address Input              |                                                                                               |

| 27    | A8      | $V_{DD}$ | Power Supply               |                                                                                               |

| 28    | NC      | DC       | Do Not Connect             | This pin is used for test. Recommend to float. If driven, must be pulled to $V_{\text{IL}}$ . |

Table 3 - Overview: CY62136FV30LL-45BVXI vs. MR1A16ACMA35

| Parameter          | CY62136FV30LL                  | MR1A16ACMA35              |  |

|--------------------|--------------------------------|---------------------------|--|

| Package            | 48 Ball VFBGA                  | 48 Ball BGA               |  |

| Size and Height    | 6 × 8 × 1.0 mm                 | 10 x 10 x 1.35 mm         |  |

| Pinout / Footprint | See Figure 2 and Table 4 below |                           |  |

| Solder Profile     | Per JEDEC J-STD-020D.1         |                           |  |

| Firmware / Timing  | Ons Address Hold Time          | 12ns Minimum Address Hold |  |

|                    |                                | Time. See Figure 7 below  |  |

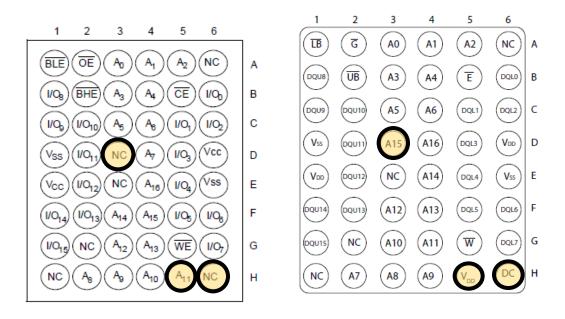

Figure 2 – Pinout/Footprint Comparison and Considerations

## **48 BALL BGA**

Table 4 – Pin Function Comparison

| Ball # | Cypress | Everspin | <b>Everspin Definition</b> | Everspin Comments                                                                             |

|--------|---------|----------|----------------------------|-----------------------------------------------------------------------------------------------|

| D3     | NC      | A15      | Address Input              |                                                                                               |

| H5     | A11     | $V_{DD}$ | Power Supply               |                                                                                               |

| H6     | NC      | DC       | Do Not Connect             | This pin is used for test. Recommend to float. If driven, must be pulled to $V_{\text{IL}}$ . |

**Cypress**

**Everspin Technologies**

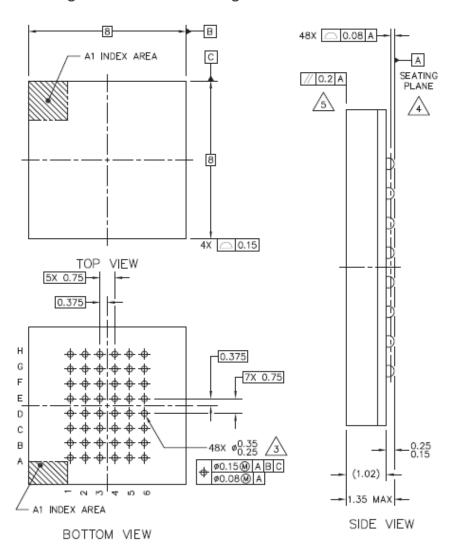

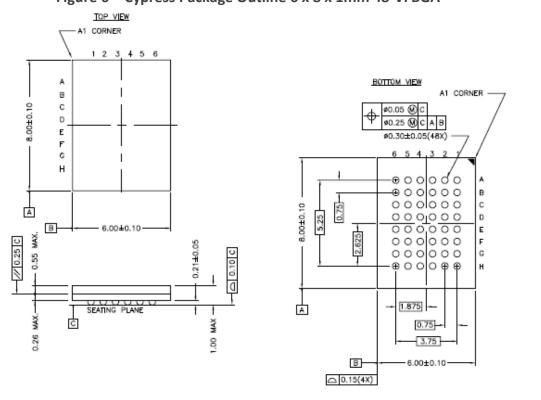

## PACKAGE COMPATIBILITY

The Everspin Technologies 44 Pin TSOP 2 package is a drop-in replacement with the corresponding Cypress equivalent (see Figure 3). The Everspin Technologies 48 Ball BGA package is a close-fit with the corresponding Cypress equivalent. However, see figures 4 and 6 to understand the package dimension differences between the Cypress and Everspin FBGA packages. Make special note of the package dimension differences requiring different mechanical "Keep out" areas for these packages. Please refer to the current datasheet for details.

0.05 0.15

NEW D

♦ 0.200 CA

SECTION E-E

Figure 4 - EVERSPIN Package Outline 10x10mm 48-BGA

Figure 5 - Cypress 44-pin TSOP Z44-II Package Outline 8888888888888888888888 <u>ÄRRARARARARARARARAR</u>AÀ (0,404) (0.452) 11.938 EJECTOR MARK (OPTIONAL) CAN BE LOCATED ANYWHERE IN THE BOTTOM VIEW TOP VIEW BOTTOM PKG 0.800 BSC\_ (0.0315) BASE PLANE 0.10 (.004) 0.210 (0.0083) 0.991 (0.039) SEATING DIMENSION IN MM (INCH) MAX PKG WEIGHT: REFER TO PMDD SPEC

Figure 6 - Cypress Package Outline 6 x 8 x 1mm 48-VFBGA

### OTHER REPLACEMENT DESIGN CONSIDERATIONS

#### MRAM ADDRESS HOLD TIME

The Address Hold Time (Everspin Write Recovery Time, tWHAX) for the M1A16Axxx35 is a minimum of 12ns compared to 0ns minimum for CY62136FV30LL.

Figure 7 – 12ns Minimum for Address Hold Time for MR1A16Axxx35

#### SIMPLIFIED POWER CYCLING

When power is removed from the MRAM, data remains valid for 20 years across the full temperature range. This feature, unique to MRAM, allows for Duty Cycle Power control enabling the user to reduce their overall power consumption without concern of wear-out or lost data.

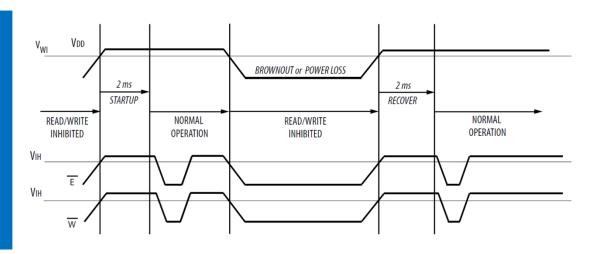

The MRAM is protected from write operations whenever  $V_{DD}$  is less than  $V_{WI}$ . As soon as  $V_{DD}$  exceeds  $V_{DD}$  (min), there is a startup time of 2 ms before read or write operations can start. This time allows memory power supplies to stabilize.

The  $\underline{E}$  and  $\underline{W}$  control signals should track  $V_{DD}$  on power up to  $V_{DD}$ - 0.2 V or  $V_{IH}$  (whichever is lower) and remain high for the startup time. In most systems, this means that these signals should be pulled up with a resistor so that a signal remains high if the driving signal is Hi-Z during power up. Any logic that drives  $\underline{E}$  and  $\underline{W}$  should hold the signals high with a power-on reset signal for longer than the startup time. During power loss or brownout where  $V_{DD}$  goes below  $V_{WI}$ , writes are protected and a startup time must be observed when power returns above  $V_{DD}$ (min).

### **MRAM POWER-UP SEQUENCING**

Both MRAM and SRAM will operate from a standard +3.3 V power supply with +/-10% power supply range. Both MRAM and SRAM have similar standby and active operating currents, however, the "Start-up" time for the MRAM is 2ms vs. 45ns for the SRAM. Proper decoupling capacitors should be used to assure reliable operation. The power loss/startup sequences for both products are shown below:

#### MORE TEMPERATURE GRADES OPTIONS

It is possible to offer additional temperature grades to replace Cypress CY62136FV30LL SRAM

- MR1A16AVYS35 (-40C to 105C Extended) as replacement for CY62136FV30LL-45ZSXA

- MR1A16AMYS35 (-40C to 125C AEC-Q100 Grade 1) as replacement for CY62136FV30LL-55ZSXE

## **SUMMARY**

Replacing a CY62136FV30LL with Everspin's M1A16Axxx35 2Mb MRAM is a straight-forward process. These devices are close to a drop-in replacement with some consideration of pinout and timing details shown in the application note.

#### **Contact Information:**

Author:

Paolo Schiappacasse

**FAE EMEA**

**Everspin Sales**

### How to Reach Us:

www.everspin.com

E-Mail:

support@everspin.com

orders@everspin.com

sales@everspin.com

#### **USA/Canada/South and Central America**

**Everspin Technologies**

5670 W. Chandler Road, Suite 100

Chandler, Arizona 85226

+1-877-347-MRAM (6726)

+1-480-347-1111

#### **Europe, Middle East and Africa**

support.europe@everspin.com

## Japan

support.japan@everspin.com

#### **Asia Pacific**

support.asia@everspin.com

## Everspin Technologies, Inc.

Information in this document is provided solely to enable system and software implementers to use Everspin Technologies products. There are no express or implied licenses granted hereunder to design or fabricate any integrated circuit or circuits based on the information in this document. Everspin Technologies reserves the right to make changes without further notice to any products herein. Everspin makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Everspin Technologies assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters, which may be provided in Everspin Technologies data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters including "Typical" must be validated for each customer application by customer's technical experts. Everspin Technologies does not convey any license under its patent rights nor the rights of others. Everspin Technologies products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Everspin Technologies product could create a situation where personal injury or death may occur. Should Buyer purchase or use Everspin Technologies products for any such unintended or unauthorized application, Buyer shall indemnify and hold Everspin Technologies and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Everspin Technologies was negligent regarding the design or manufacture of the part. Everspin™ and the Everspin logo are trademarks of Everspin Technologies, Inc. All other product or service names are the property of their respective owners.