### **SOIC PACKAGE**

## 16-pin SOIC

- Compliant with RoHS, REACH regulations and practices.

- Contain no Red Phosphorus.

- Lead Free.

- All products meet MSL-3 moisture sensitivity level.

- Standard Reflow profile.

- Compatible with similar low-power SRAM products and other nonvolatile RAM products.

## **TABLE OF CONTENTS**

| COMPLIANCE WITH ENVIRONMENTAL REGULATIONS AND DIRECTIVES           | 2 |

|--------------------------------------------------------------------|---|

| Table 1 – Environmental Regulation and Directive Compliance        | 2 |

| MULTIPLE REFLOW CYCLES AND MOISTURE RESISTANCE                     | 2 |

| RECOMMENDED REFLOW TEMPERATURES AND TIMING                         | 3 |

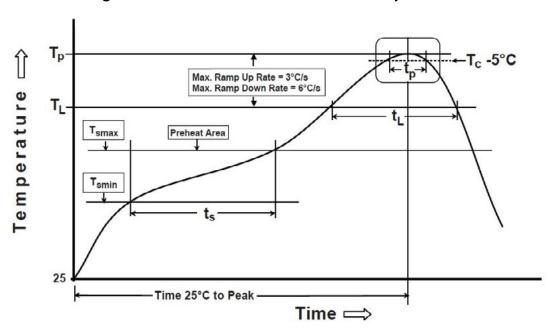

| Figure 1 – JEDEC J-STD-020D.1 Assembly Reflow Profile              | 3 |

| Table 2 – Recommended Reflow Times and Temperatures - All Packages | 3 |

| THERMAL RESISTANCE                                                 | 4 |

| Table 3 – Thermal Resistance 16-pin SOIC                           | 4 |

| PACKAGE OUTLINE DRAWINGS                                           | 5 |

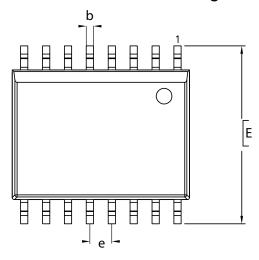

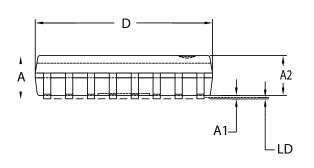

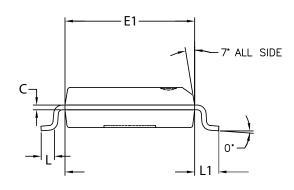

| Figure 2 – Package Outline 16-pin SOIC                             | 5 |

| REVISION HISTORY                                                   | 6 |

| CONTACT US                                                         | 7 |

### **COMPLIANCE WITH ENVIRONMENTAL REGULATIONS AND DIRECTIVES**

Table 1 – Environmental Regulation and Directive Compliance

| Environment            | Statement Summary                                                                                                                                                                                                                                                                                                                                                    | Download Full State-<br>ment |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|

| ISO9001:2008           | Everspin Technologies is in conformance with ISO9001:2008                                                                                                                                                                                                                                                                                                            | <u>Certificate</u>           |  |

| RoHS Directives        | Statement of RoHS 1 and the recast Directive 2011/65/EU is commonly referred to as RoHS 2 Compliance. Everspin MRAM products are also "halogen-free".                                                                                                                                                                                                                | Full Statement               |  |

| REACH Regula-<br>tions | REACH regulations require article suppliers to inform recipients if an article contains a Substance of Very High Concern (SVHC) in excess of 0.1% by weight.  Based on the material content certifications provided by Everspin's suppliers, none of these substances are present in the materials we use in our products, including packing and shipping materials. | Full Statement               |  |

| Red Phosphorus         | Everspin Technologies, Inc. MRAM products do not contain Red Phosphorus CAS# 7723-14-0 as an intentional additive.                                                                                                                                                                                                                                                   | Full Statement               |  |

### MULTIPLE REFLOW CYCLES AND MOISTURE RESISTANCE

All Everspin packages are qualified by the procedure defined in IPC/JEDEC joint specification IPC/JEDEC J-STD-020D.1. They are guaranteed to withstand up to three reflow cycles without permanent damage, provided the conditions for the rated moisture resistance level for the part are observed prior to reflow.

Everspin parts are generally rated for MSL Level 3. Exceptions may exist and are noted in their respective data sheet. Please the check the latest individual product data sheet to confirm the rated MSL for the product.

### RECOMMENDED REFLOW TEMPERATURES AND TIMING

Everspin products can be assembled using a standard assembly lead-free reflow profile. The profile below is based on IPC/JEDEC J-STD-020D.1.

Figure 1 – JEDEC J-STD-020D.1 Assembly Reflow Profile

Table 2 – Recommended Reflow Times and Temperatures - All Packages

| Profile Step   | Parameter                                          | Symbol             | Time/Temp     | Unit    |

|----------------|----------------------------------------------------|--------------------|---------------|---------|

|                | Temperature mininumum                              | T <sub>SMIN</sub>  | 150           | °C      |

| Preheat / Soak | Temperature maximum                                | T <sub>SMAX</sub>  | 200           | °C      |

|                | Soak Time                                          | tς                 | 60 - 120      | Seconds |

| Ramp Up        | Rate from $T_L$ to $T_P$                           | $T_L$ to $T_P$     | 3° / Sec Max  | °/Sec   |

|                | 25°C to T <sub>P</sub>                             |                    | 8 minutes max | Minutes |

|                | Liquidous Temperature                              | $T_L$              | 217           | °C      |

|                | Time Above T <sub>L</sub>                          |                    | 60 - 150      | Seconds |

| Reflow         | Peak Package Body Tempera-<br>ture                 | T <sub>P</sub>     | 260           | °C      |

|                | Time within 5° of Peak Package<br>Body Temperature |                    | 20 - 40       | Seconds |

| Ramp Down      | Rate from T <sub>P</sub> to T <sub>L</sub>         | $T_{p}$ to $T_{L}$ | 6° / Sec Max  | °/Sec   |

## THERMAL RESISTANCE

Table 3 – Thermal Resistance 16-pin SOIC

| Velocity<br>(m/s) | T <sub>A</sub> (°C) | Power<br>(W)                                     | T <sub>J</sub> Max ° <b>C</b> | Θ <sub>JA</sub><br>(°C/W) | Θ <sub>JB</sub> | Θ <sub>JC</sub><br>(°C/W) | Ψ <sub>JB</sub><br>(°C/W) | Θ <sub>JT</sub><br>(°C/W) |      |

|-------------------|---------------------|--------------------------------------------------|-------------------------------|---------------------------|-----------------|---------------------------|---------------------------|---------------------------|------|

| 0                 | 25                  | 71.0 58.1<br>64.5 49.9<br>62.8 47.7<br>61.8 46.4 |                               |                           | 2.0             | 30.6                      |                           |                           |      |

| 1                 |                     |                                                  | 64.5                          | 49.9                      | 30.6            | 21.6                      | 2.8                       | 29.6                      |      |

| 2                 |                     |                                                  | 62.8                          | 47.7                      |                 | 30.0                      | 31.6                      | 3.2                       | 29.1 |

| 3                 |                     |                                                  | 61.8                          | 46.4                      |                 |                           | 3.5                       | 28.8                      |      |

### **PACKAGE OUTLINE DRAWINGS**

Figure 2 – Package Outline 16-pin SOIC

| Symbol | JEDEC MS - 013 (AA) |     |      | Everspin                     | POD 16L SOIC PK | G OUTLINE |

|--------|---------------------|-----|------|------------------------------|-----------------|-----------|

|        | issue (mm)          |     |      | issue (mm) DWG. 300 MIL (mm) |                 |           |

| Ref    | MIN                 | NOM | MAX  | MIN                          | NOM             | MAX       |

| Α      | -                   | -   | 2.65 | 2.46                         | 2.56            | 2.64      |

| A1     | 0.10                | -   | 0.30 | 0.127                        | 0.22            | 0.29      |

| A2     | 2.05                | -   | -    | 2.29                         | 2.34            | 2.39      |

| b      | 0.31                | -   | 0.51 | 0.35                         | 0.41            | 0.51      |

| С      | 0.20                | -   | 0.33 | 0.23                         | 0.25            | 0.32      |

| D      | 10.30 BSC           |     |      | 10.21                        | 10.34           | 10.46     |

| Е      | 10.30 BSC           |     |      | 10.16                        | 10.31           | 10.63     |

| E1     | 7.50 BSC            |     |      | 7.44                         | 7.52            | 7.59      |

| L      | 0.40                | -   | 1.27 | 0.61                         | 0.81            | 1.02      |

| L1     | 1.40 REF            |     |      |                              | N/A             |           |

| е      | 1.27 BSC            |     |      |                              | 1.27 BSC        |           |

| Θ      | 0°                  | -   | 8°   | 0°                           | 5°              | 8°        |

# **Everspin SOIC MRAM Package Guide**

## **REVISION HISTORY**

| Revision | Date              | Description of Change                                   |  |

|----------|-------------------|---------------------------------------------------------|--|

| 1.0      | Oct 7, 2013       | Initial release                                         |  |

| 1.1      | Oct 21, 2014      | Added Reflow Cycle and Moisture Resistance section.     |  |

| 1.2      | February 24, 2015 | Added matte Sn plating thickness.                       |  |

| 2.0      | August 6, 2015    | Removed 32-SOIC Package. Reference PCN 02895.           |  |

| 2.1      | December 1, 2017  | Updated package dimension table and drawing in Figure 2 |  |

| 2.2      | March 22, 2018    | Contact information table updated                       |  |

### **CONTACT US**

### **Home Page:**

www.everspin.com

#### **World Wide Information Request**

#### WW Headquarters - Chandler, AZ

5670 W. Chandler Blvd., Suite 100

Chandler, Arizona 85224

Tel: +1-877-480-MRAM (6726)

Local Tel: +1-480-347-1111

Fax: +1-480-347-1175

support@everspin.com

#### **Europe, Middle East and Africa**

**Everspin Europe Support**

support.europe@everspin.com

#### **Japan**

**Everspin Japan Support**

support.japan@everspin.com

#### **Asia Pacific**

**Everspin Asia Support**

support.asia@everspin.com

EST02614\_SOIC Package Guide\_Revision2.2 032218

## **Everspin Technologies, Inc.**

Information in this document is provided solely to enable system and software implementers to use Everspin Technologies products. There are no express or implied licenses granted hereunder to design or fabricate any integrated circuit or circuits based on the information in this document. Everspin Technologies reserves the right to make changes without further notice to any products herein. Everspin makes no warranty, representation or quarantee regarding the suitability of its products for any particular purpose, nor does Everspin Technologies assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters, which may be provided in Everspin Technologies data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters including "Typicals" must be validated for each customer application by customer's technical experts. Everspin Technologies does not convey any license under its patent rights nor the rights of others. Everspin Technologies products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Everspin Technologies product could create a situation where personal injury or death may occur. Should Buyer purchase or use Everspin Technologies products for any such unintended or unauthorized application, Buyer shall indemnify and hold Everspin Technologies and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Everspin Technologies was negligent regarding the design or manufacture of the part. Everspin™ and the Everspin logo are trademarks of Everspin Technologies, Inc. All other product or service names are the property of their respective owners.

Copyright © 2018 Everspin Technologies, Inc.