This Application Note is to inform Everspin customers that a new, DFN8 package with a 2mm bottom exposed pad has been added to EVERSPIN's family of SPI products. This new package allows the device to be used on both JEDEC standard SOIC-8 pin as well as DFN8 PCB Land Patterns. When ordering SPI devices with the smaller exposed pad, please us the "DF" suffix. Figure 1 shows a typical SOIC-8 PCB land pattern.

### **BACKGROUND**

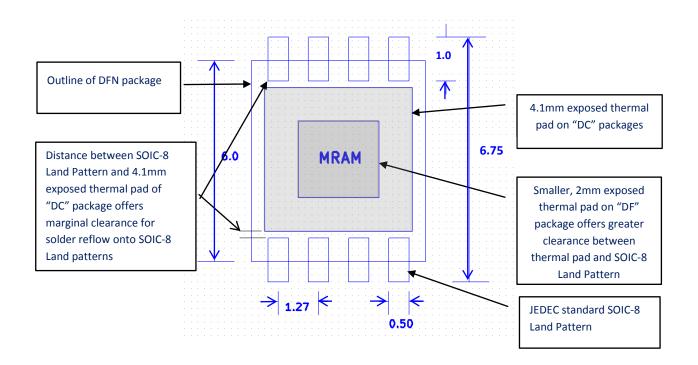

Some Everspin customers have expressed concern about marginal clearance between the exposed bottom pad of the Everspin "DC" DFN package (4.1mm pad), and the PCB pads for an SOIC-8 package. This concern is alleviated with Everspin's new 2mm exposed pad DFN-8 package.

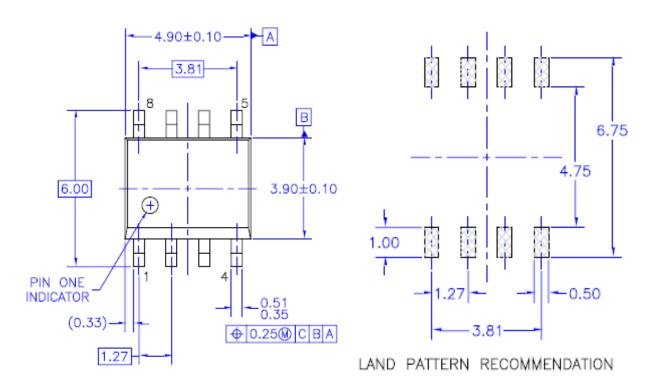

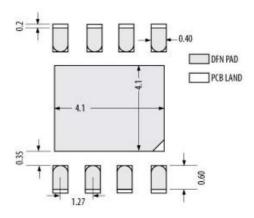

**Figure 1** typifies approximate dimensions and recommended PCB Land Pattern for a JEDEC standard SOIC-8 package (Note: the below dimensions are approximate and may vary by supplier)

Figure 1 - Package Dimension and Land Pattern for 8 pin SOIC

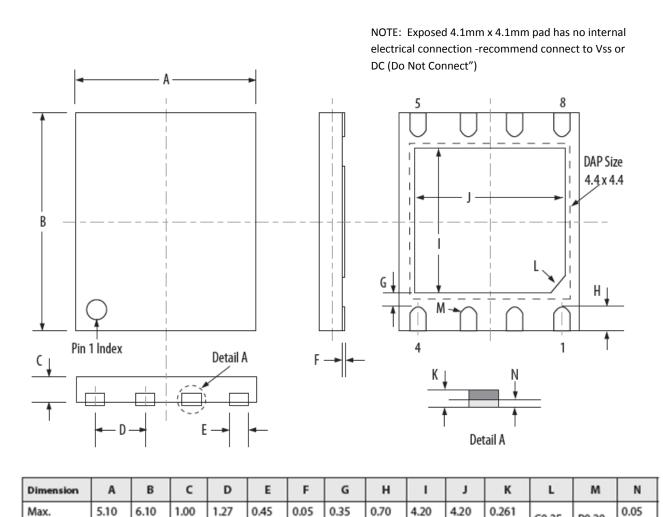

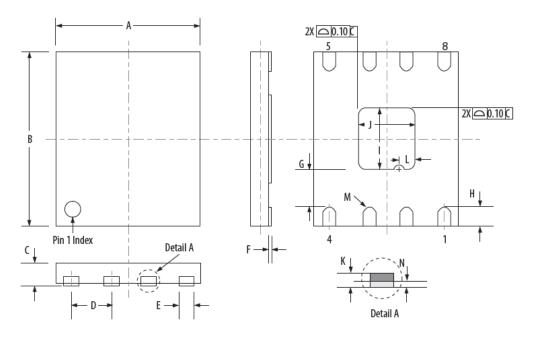

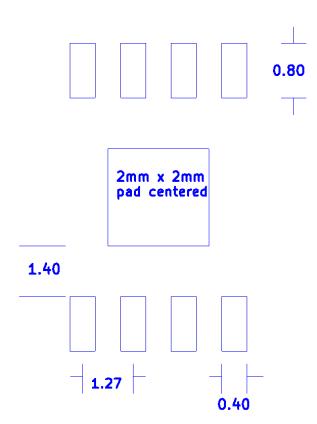

Figures 2 and 3 are package dimensions for the Everspin MR25HxxxDC (4.1mm exposed bottom pad) and MR25HxxxDF (2.0mm exposed bottom pad) packages respectively. Due to the marginal clearance between the 4.1mm exposed bottom pad of the MR25HxxxDC and the SOIC-8 PCB land pattern, the new package with a 2.0mm exposed bottom pad (MR25HxxxDF) has been approved for production by Everspin and is compatible with both JEDEC standard SOIC-8 and DFN-8 Land Patterns. The smaller bottom pad offers adequate clearance between the bottom pad and the PCB land pattern of the SOIC-8.

Figure 2 - Package Dimensions for Everspin MR25HxxxDC Package

Ref.

0.50

4.00

4.00

0.195

0.00

C0.35

Document Number: 02153 4/2013

R0.20

0.00

5.90

0.90

BSC

0.35

4.90

Min.

NOTE: Exposed 2mmx2mm pad has no internal electrical connection - recommend connect to Vss or DC (Do Not Connect")

| Dimension | А    | В    | С    | D          | E    | F    | G    | Н    | I    | J    | К    | L     | M     | N    |

|-----------|------|------|------|------------|------|------|------|------|------|------|------|-------|-------|------|

| Max       | 5.10 | 6.10 | 0.90 | 1 27 RSC 1 | 0.45 | 0.05 | 1.60 | 0.70 | 2.10 | 2.10 | .210 | C0.45 | R0.20 | 0.05 |

| Min       | 4.90 | 5.90 | 0.80 |            | 0.35 | 0.00 | 1.20 | 0.50 | 1.90 | 1.90 | .196 |       |       | 0.00 |

Figure 3 - Package Dimension for Everspin's MR25HxxxDF Package

**Figure 4** illustrates marginal clearance between the JEDEC standard SOIC-8 Land Pattern and the 4.1mm exposed pad on the bottom of the MR25HxxxDF DFN package against the additional clearance offered by the smaller, 2mm exposed pad of the MR25HxxxDF package.

Figure 4 - Dimensions of Everspin's "DC" vs. "DF" packages on JEDEC SOIC-8 Land Pattern

(Note 1: All dimensions in mm)

Figure 5 is the recommended PCB Land Pattern for Everspin's "DC" DFN-8 packages. This Land Pattern will accommodate both the MR25HxxxDC as well as the MR25HxxxDF packages. Note that it is acceptable to mount a "DF" package on the 4.1mm x 4.1mm Land Pattern (recommended for the MR25HxxxDC packages), however figure 6 is the recommended Land Pattern for the MR25HxxxDF packages (2mm exposed pad).

Figure 5: Everspin's recommended Land Pattern for the "DC" package.

(Note that it is acceptable to mount the "DF" package on the 4.1mm x 4.1mm Land Pattern recommended for the "DC" package, however figure 6 is the recommended Land Pattern for the "DF" package

(All units in mm)

Figure 6: Recommended PCB Land Pattern for Everspin's MR25HxxxDF packages.

(All units in mm)

#### How to Reach Us:

Home Page: www.everspin.com

#### E-Mail:

support@everspin.com orders@everspin.com sales@everspin.com

#### **USA/Canada/South and Central America**

Everspin Technologies 1347 N. Alma School Road, Suite 220 Chandler, Arizona 85224 +1-877-347-MRAM (6726) +1-480-347-1111

### Europe, Middle East and Africa support.europe@everspin.com

### Japan

support.japan@everspin.com

#### **Asia Pacific**

support.asia@everspin.com

### **Everspin Technologies, Inc.**

Information in this document is provided solely to enable system and software implementers to use Everspin Technologies products. There are no express or implied licenses granted hereunder to design or fabricate any integrated circuit or circuits based on the information in this document. Everspin Technologies reserves the right to make changes without further notice to any products herein. Everspin makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Everspin Technologies assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters, which may be provided in Everspin Technologies data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters including "Typical" must be validated for each customer application by `-customer's technical experts. Everspin Technologies does not convey any license under its patent rights nor the rights of others. Everspin Technologies products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Everspin Technologies product could create a situation where personal injury or death may occur. Should Buyer purchase or use Everspin Technologies products for any such unintended or unauthorized application, Buyer shall indemnify and hold Everspin Technologies and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Everspin Technologies was negligent regarding the design or manufacture of the part. Everspin™ and the Everspin logo

Document Number: 02153 4/2013

are trademarks of Everspin Technologies, Inc. All other product or service names are the property of their respective owners.

Copyright © 2013 Everspin Technologies, Inc.

### EVERSPIN's new, 2mm Exposed Pad DFN package meets both SOIC-8 and DFN8 PCB Layouts

Author: Chuck Bohac, Manager Applications Engineering, Everspin Technologies chuck.bohac@everspin.com, 480-347-1161